AMCC Proprietary 143

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

8.8.1 Debug Control Registers

The debug control registers (DBCR0 and DBCR1)can enable and configure debug events, reset the processor,

control timer operation during debug events, enable debug interrupts, and set the processor debug mode.

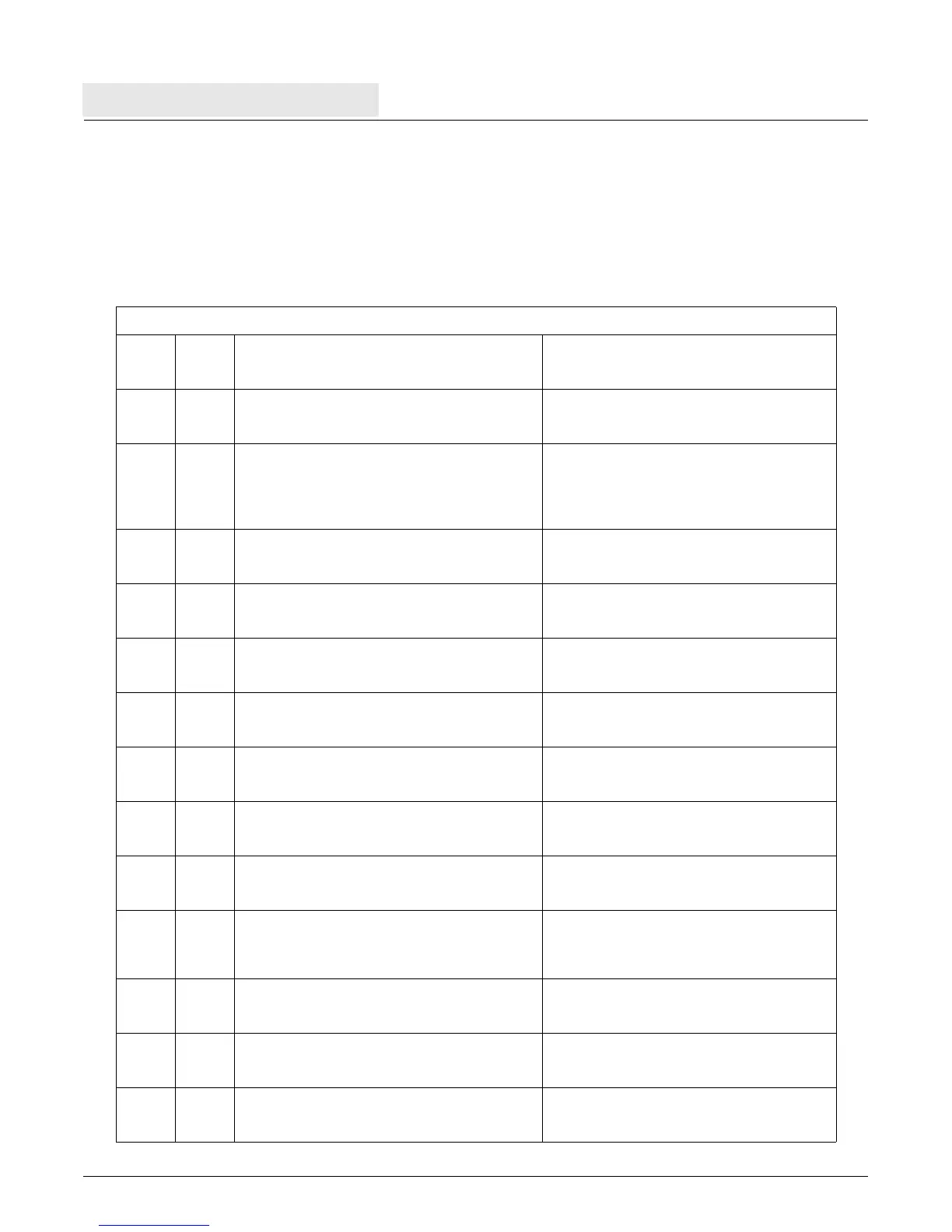

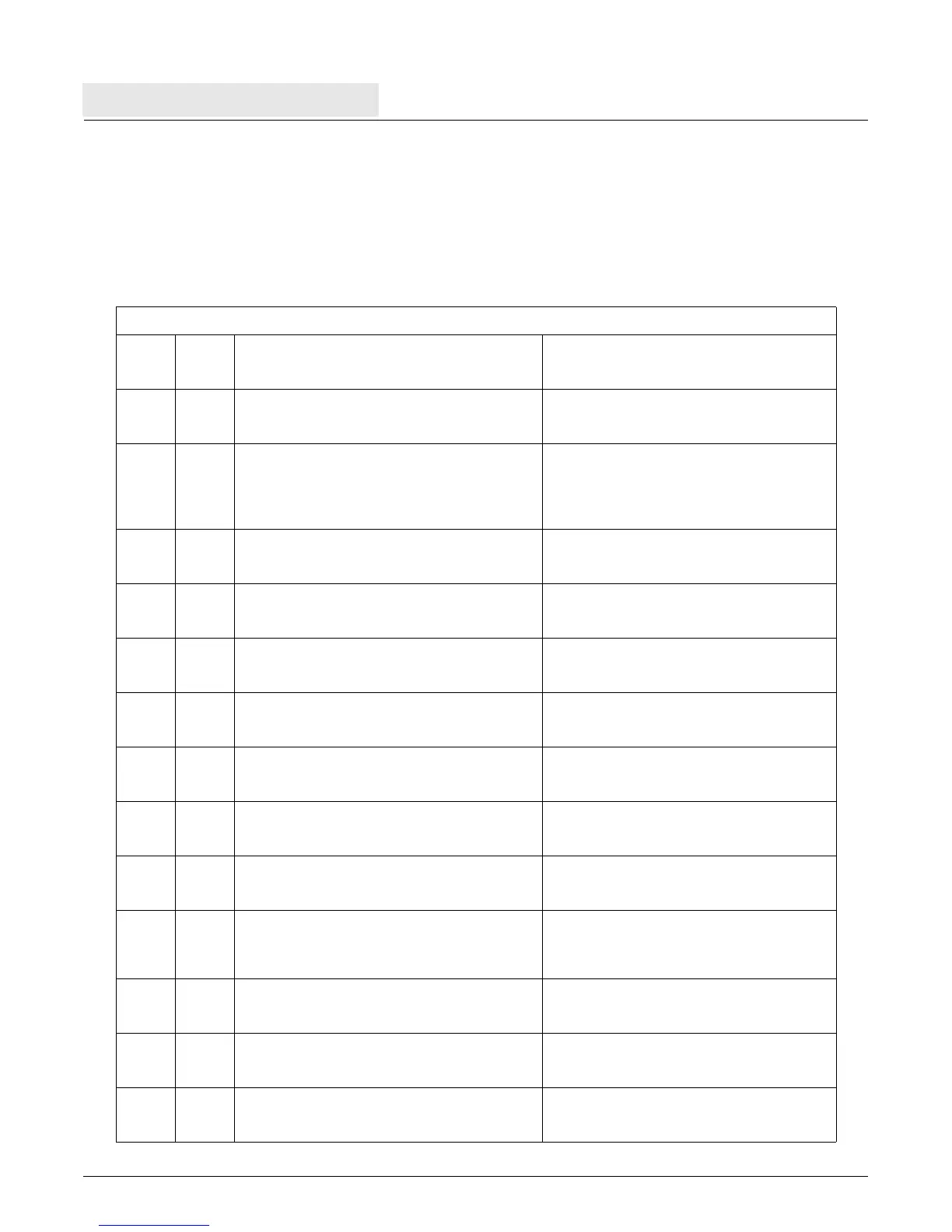

8.8.1.1 Debug Control Register 0 (DBCR0)

Figure 8-1. Debug Control Register 0 (DBCR0)

0EDM

External Debug Mode

0 Disabled

1 Enabled

1IDM

Internal Debug Mode

0 Disabled

1 Enabled

2:3 RST

Reset

00 No action

01 Core reset

10 Chip reset

11 System reset

Causes a processor reset request when set by

software.

Attention: Writing 01, 10, or 11 to this field

causes a processor reset request.

4IC

Instruction Completion Debug Event

0 Disabled

1 Enabled

5BT

Branch Taken Debug Event

0 Disabled

1 Enabled

6EDE

Exception Debug Event

0 Disabled

1 Enabled

7TDE

Trap Debug Event

0 Disabled

1 Enabled

8IA1

IAC 1 Debug Event

0 Disabled

1 Enabled

9IA2

IAC 2 Debug Event

0 Disabled

1 Enabled

10 IA12

Instruction Address Range Compare 1–2

0 Disabled

1 Enabled

Registers IAC1 and IAC2 define an address range

used for IAC address comparisons.

11 IA12X

Enable Instruction Address Exclusive Range Com-

pare 1–2

0Inclusive

1 Exclusive

Selects the range defined by IAC1 and IAC2 to be

inclusive or exclusive.

12 IA3

IAC 3 Debug Event

0 Disabled

1 Enabled

13 IA4

IAC 4 Debug Event

0 Disabled

1 Enabled

14 IA34

Instruction Address Range Compare 3–4:

0 Disabled

1 Enabled

Registers IAC3 and IAC4 define an address range

used for IAC address comparisons.

Loading...

Loading...