AMCC Proprietary 129

Revision 1.01 - February 19, 2007

PPC405 Processor

Preliminary User’s Manual

7. Timer Facilities

The PPC405 processor core provides four timer facilities: a time base, a Programmable Interval Timer (PIT), a

fixed interval timer (FIT), and a watchdog timer. The PIT is a Special Purpose Register (SPR). These facilities,

which are driven by the same base clock, can, among other things, be used for:

• Time-of-day functions

• Data logging functions

• Peripherals requiring periodic service

• Periodic task switching

Additionally, the watchdog timer can help a system to recover from faulty hardware or software.

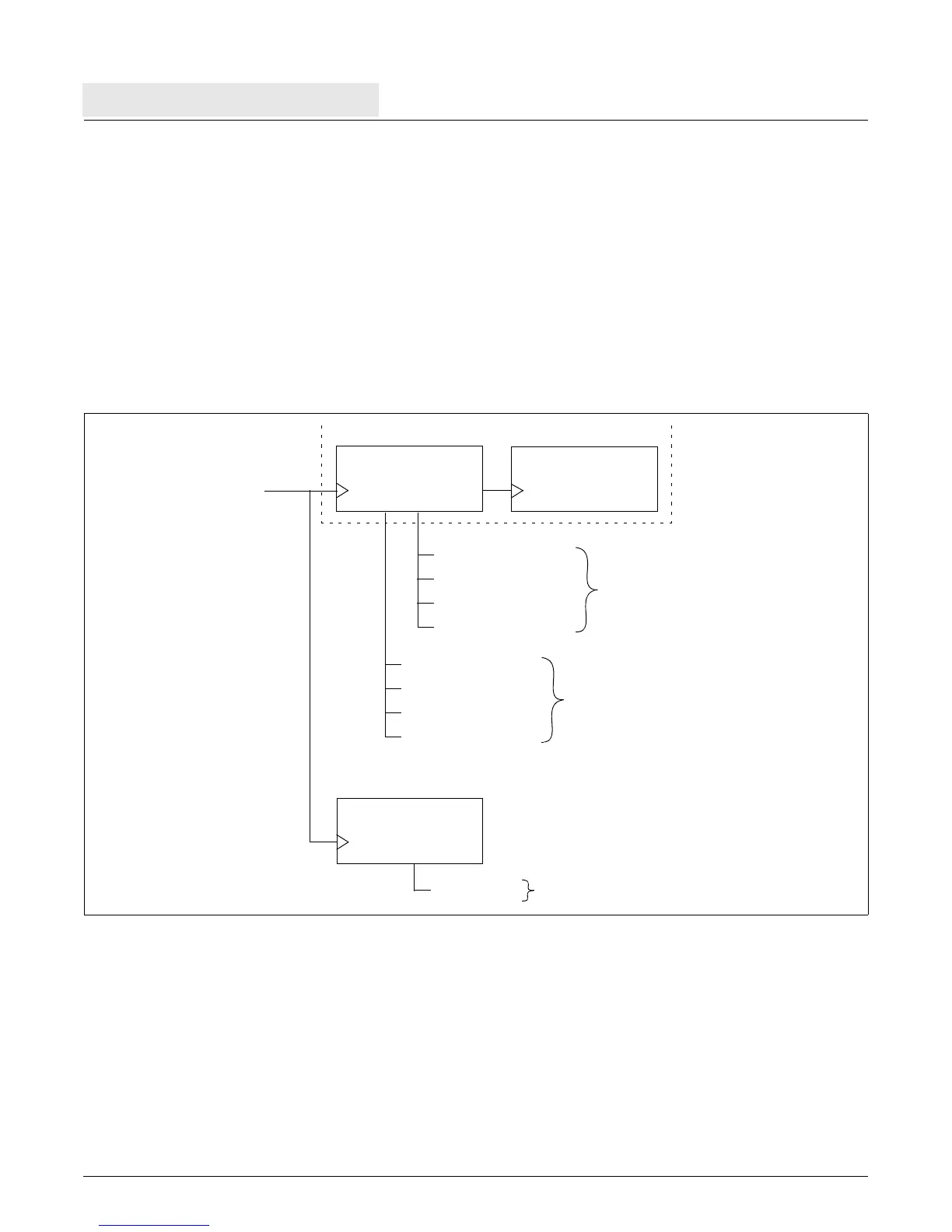

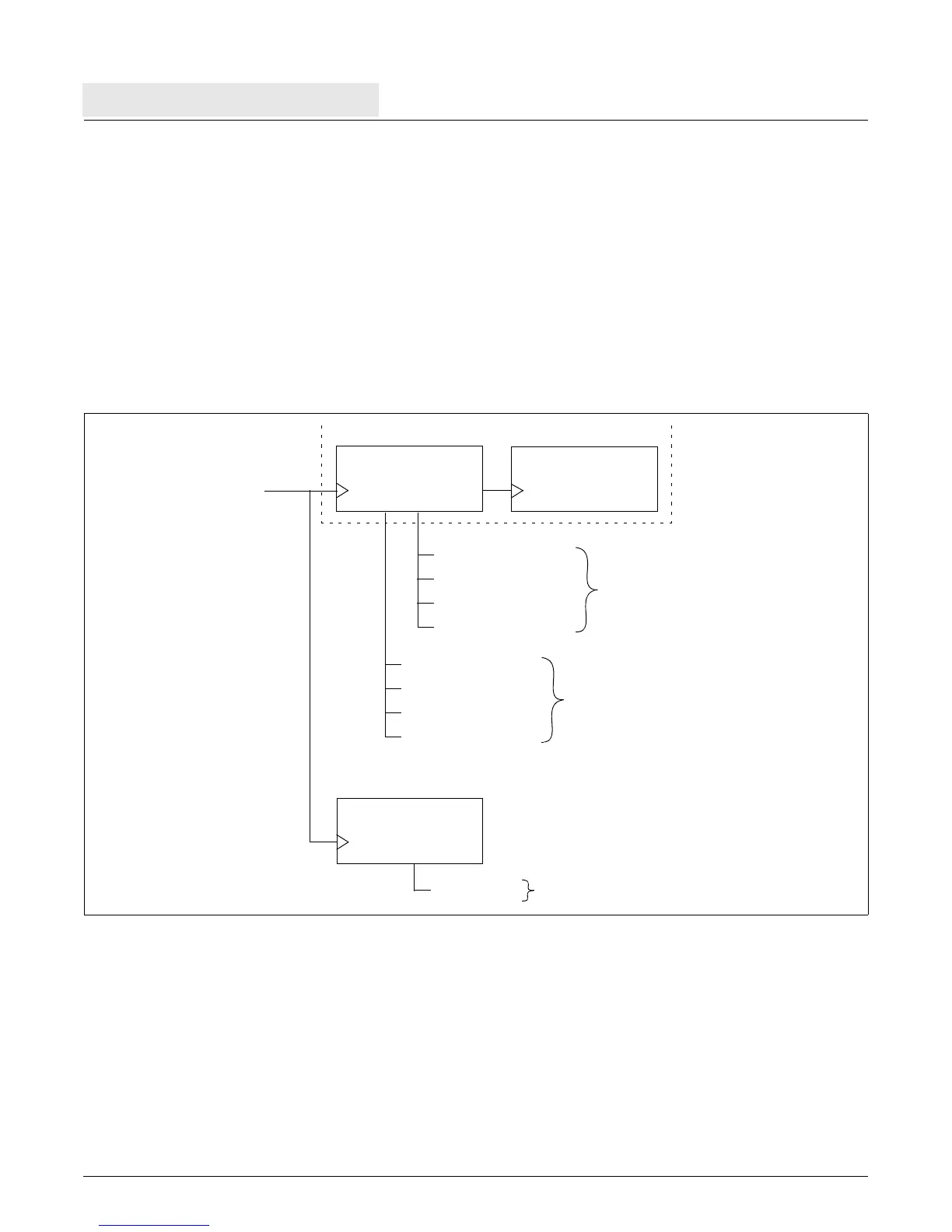

Figure 7-1 shows the relationship of the timers and the clock source to the time base.

Figure 7-1. Relationship of Timer Facilities to the Time Base

TBU (32 bits)

Bit 3 (2

29

clocks)

Bit 7 (2

25

clocks)

Bit 11 (2

21

clocks)

Bit 15 (2

17

clocks)

Bit 11

(2

21

clocks)

Bit 15

(2

17

clocks)

Bit 19

(2

13

clocks)

Bit 23

(2

9

clocks)

Watchdog Timer Events

FIT Events

Time Base (Incrementer)

31

TBL (32 bits)

31 0

0

PIT (Decrementer)

(32 bits)

31

0

Zero Detect PIT Events

Clock Source

- CPU for 405EZ

- OPB for 405EX

Loading...

Loading...