AMCC Proprietary 424

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

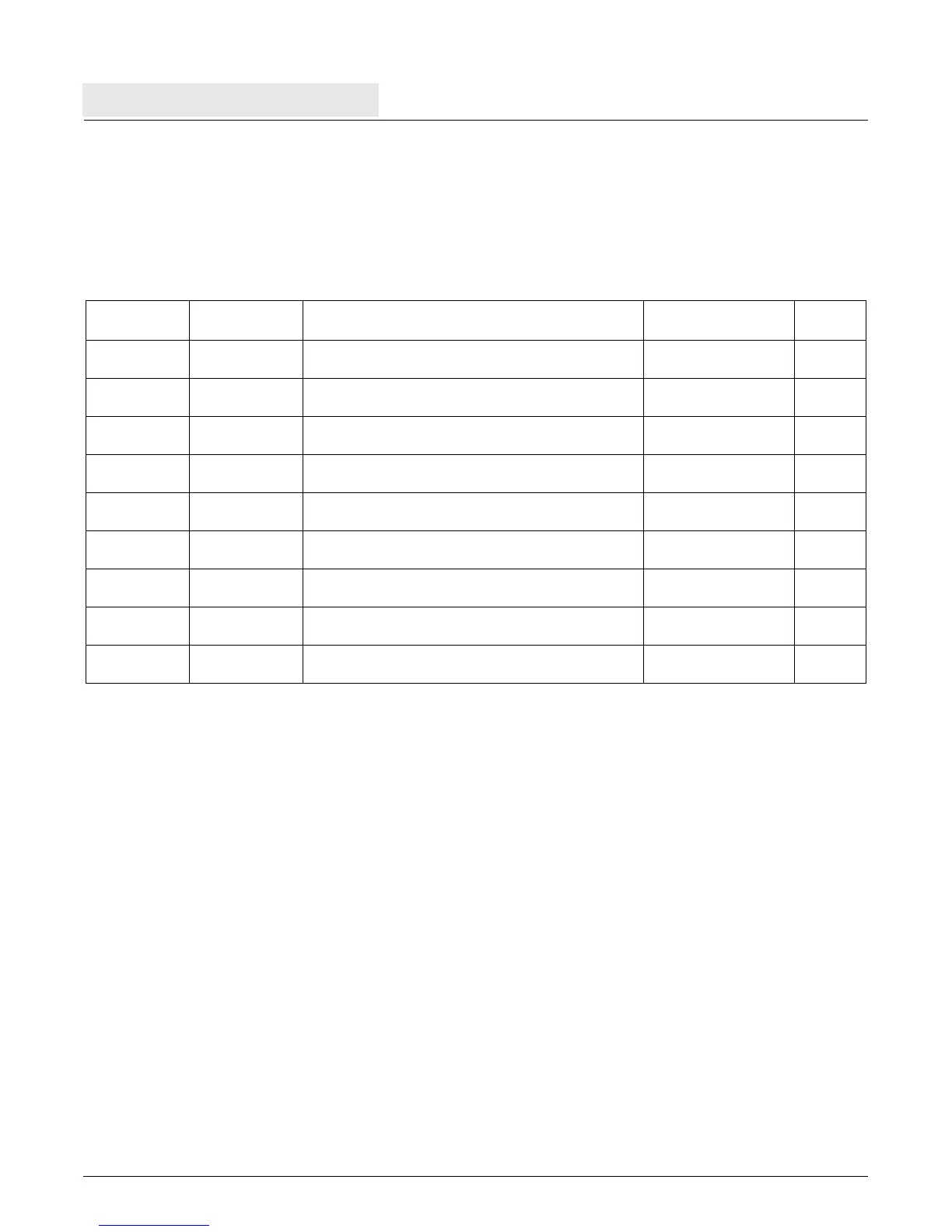

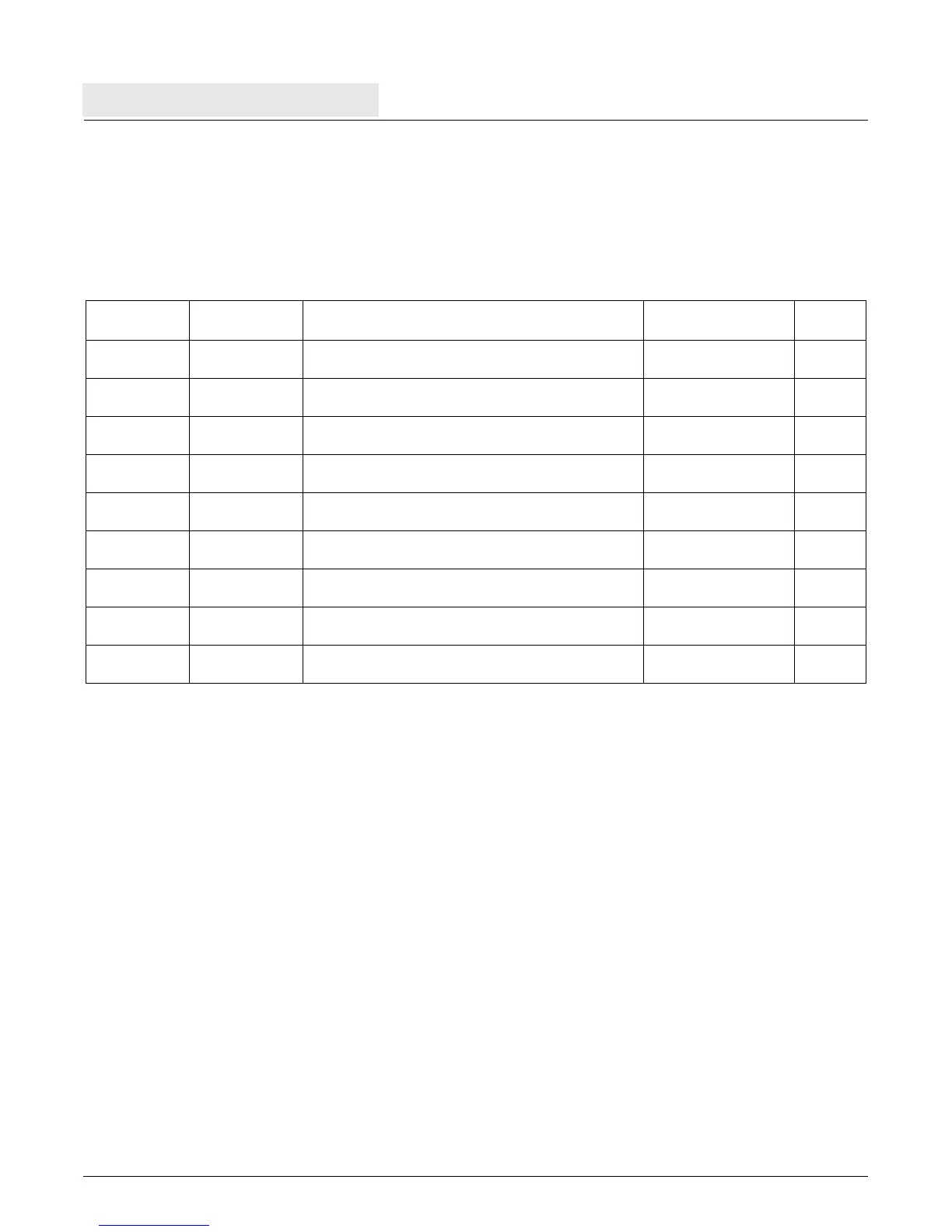

B.7 Condition Register Logical Instructions

CR logical instructions combine the results of several comparisons without incurring the overhead of conditional

branching. These instructions can significantly improve code performance if multiple conditions are tested before

making a branch decision. Table B-8 summarizes the CR logical instructions.

B.8 Branch Instructions

The architecture provides conditional and unconditional branches to any storage location. The conditional branch

instructions test condition codes set previously and branch accordingly. Conditional branch instructions may

decrement and test the Count Register (CTR) as part of determination of the branch condition and may save the

return address in the Link Register (LR). The target address for a branch may be a displacement from the current

instruction address (CIA), or may be contained in the LR or CTR, or may be an absolute address.

Table B-8. Condition Register Logical Instructions

Mnemonic Operands Function

Other Registers

Changed

Page

crand BT, BA, BB AND bit (CR

BA

) with (CR

BB

).

Place result in CR

BT

.

193

crandc BT, BA, BB AND bit (CR

BA

) with ¬(CR

BB

).

Place result in CR

BT

.

194

creqv BT, BA, BB Equivalence of bit CR

BA

with CR

BB

.

CR

BT

←¬(CR

BA

⊕ CR

BB

)

195

crnand BT, BA, BB NAND bit (CR

BA

) with (CR

BB

).

Place result in CR

BT

.

196

crnor BT, BA, BB NOR bit (CR

BA

) with (CR

BB

).

Place result in CR

BT

.

197

cror BT, BA, BB OR bit (CR

BA

) with (CR

BB

).

Place result in CR

BT

.

198

crorc BT, BA, BB OR bit (CR

BA

) with ¬ (CR

BB

).

Place result in CR

BT

.

199

crxor BT, BA, BB XOR bit (CR

BA

) with (CR

BB

).

Place result in CR

BT

.

200

mcrf BF, BFA Move CR field, (CR[CRn]) ← (CR[CRm])

where m ← BFA and n ← BF.

263

Loading...

Loading...