AMCC Proprietary 62

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

2.11.1 Instructions Specific to the PowerPC Embedded Environment

To support functions required in embedded real-time applications, the PowerPC processors define instructions that

are not defined in the PowerPC Architecture.

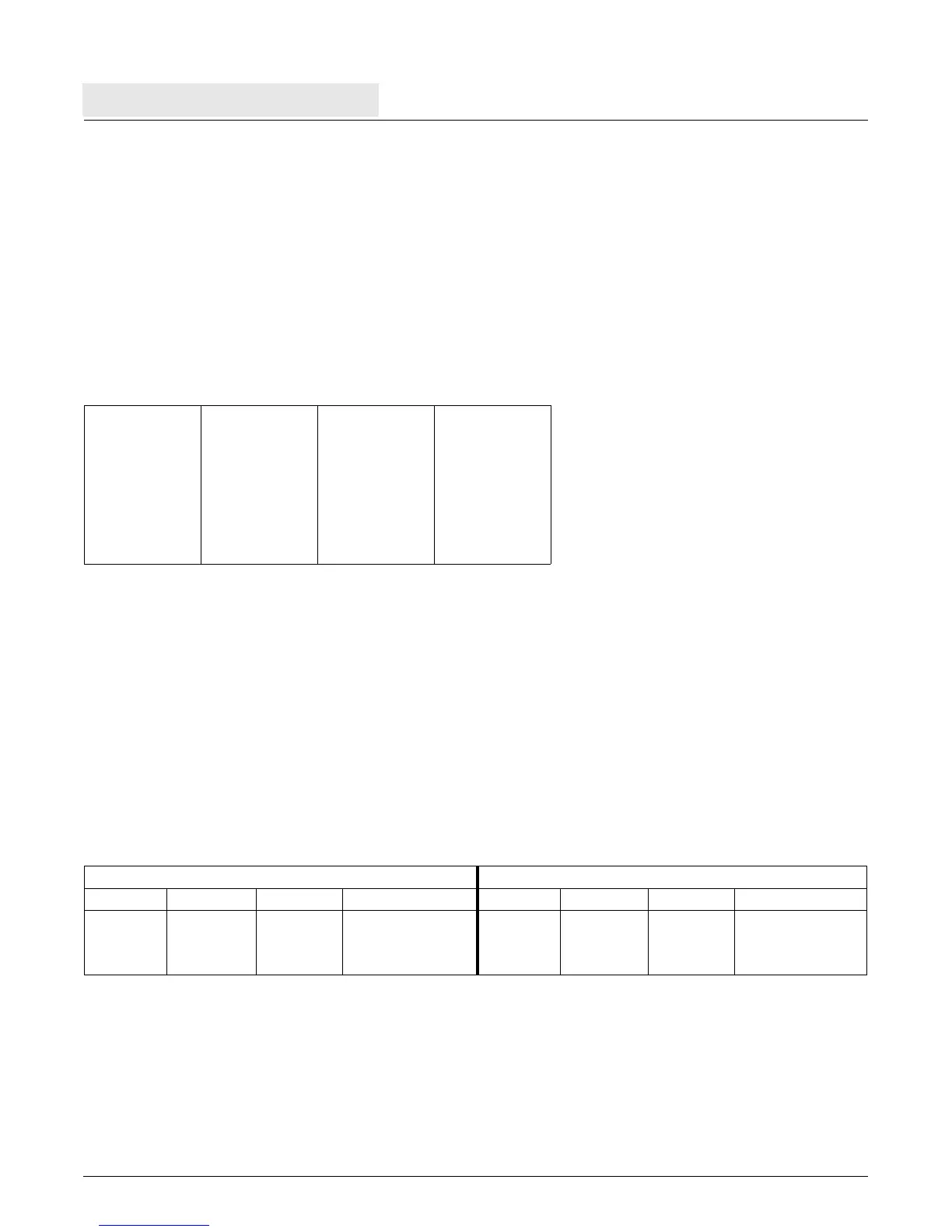

Table 2-13 lists the instructions specific to PowerPC embedded processors. Programs using these instructions are

not portable to PowerPC implementations that are not part of the PowerPC 400 family of embedded processors.

In the table, the syntax [s] indicates that the instruction has a signed form. The syntax [u] indicates that the

instruction has an unsigned form. The syntax [.] indicates that the instruction has a “record” form that updates

CR[CR0], and a “non-record” form.

2.11.2 Storage Reference Instructions

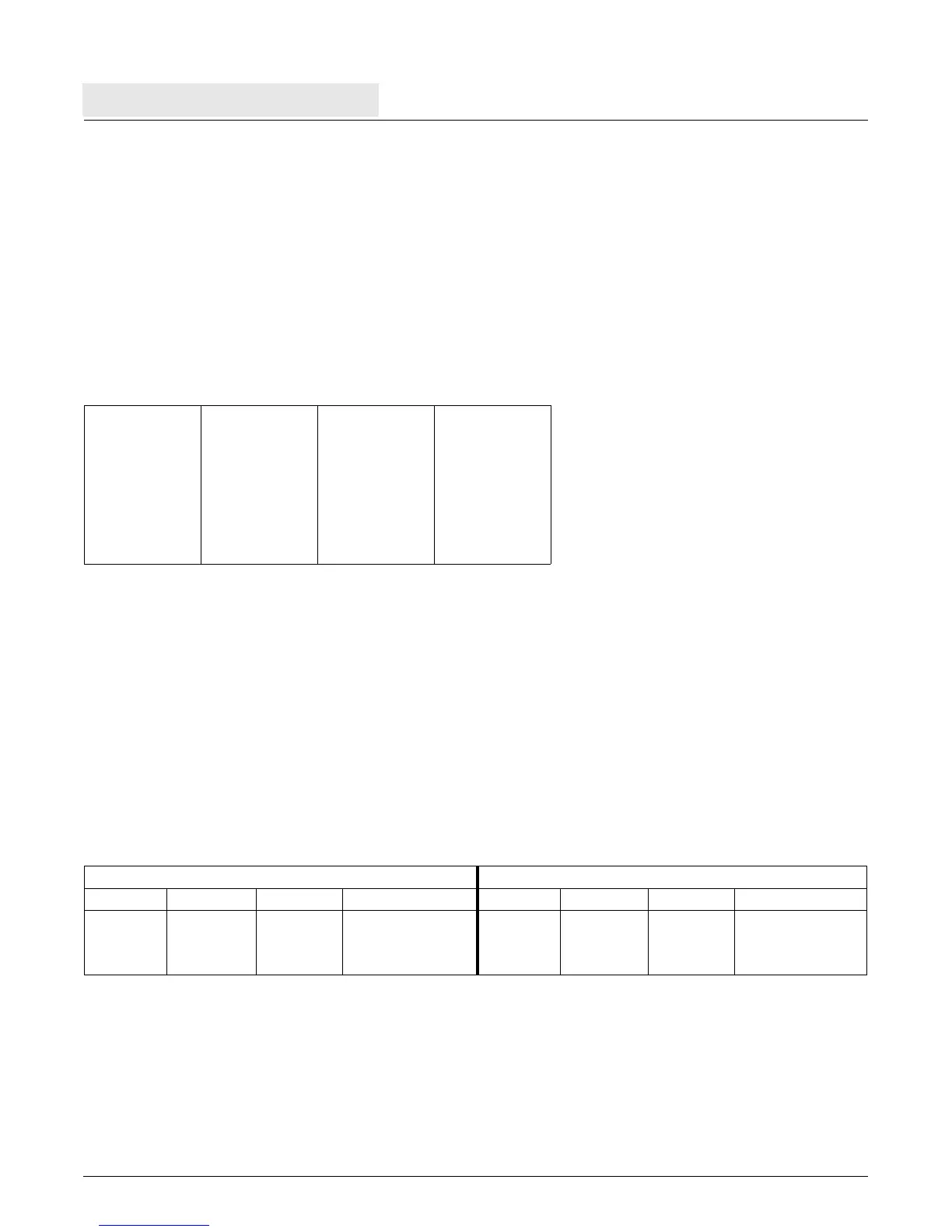

Table 2-14 lists the PPC405 storage reference instructions. Load/store instructions transfer data between memory

and the GPRs. These instructions operate on bytes, halfwords, and words. Storage reference instructions also

support loading or storing multiple registers, character strings, and bytereversed data.

In the table, the syntax [u] indicates that an instruction has an “update” form that updates the RA addressing

register with the calculated address, and a “non-update” form. The syntax [x] indicates that an instruction has an

“indexed” form, which forms the address by adding the contents of the RA and RB GPRs and a “base +

displacement” form, in which the address is formed by adding a 16-bit signed immediate value (included as part of

the instruction word) to the contents of RA GPR.

Table 2-13. Implementation-specific Instructions

dccci

dcread

iccci

icread

macchw

[s][u]

machhw[s][u]

maclhw[s][u]

nmacchw[s]

nmachhw[s]

nmaclhw[s]

mulchw[u]

mulhhw[u]

mullhw[u]

mfdcr

mtdcr

rfci

tlbre

tlbsx

[.]

tlbwe

wrtee

wrteei

Table 2-14. Storage Reference Instructions

Loads Stores

Byte Halfword Word Multiple/String Byte Halfword Word Multiple/String

lbz[u][x]

lha[u][x]

lhbrx

lhz

[u][x]

lwarx

lwbrx

lwz

[u][x]

lmw

lswi

lswx

stb

[u][x]

sth[u][x]

sthbrx

stw

[u][x]

stwbrx

stwcx.

stmw

stswi

stswx

Loading...

Loading...