AMCC Proprietary 300

Revision 1.02 - September 10, 2007

PPC405 Processor

rlwinm

Rotate Left Word Immediate then AND with Mask

Preliminary User’s Manual

rlwinm

Rotate Left Word Immediate then AND with Mask

r ← ROTL((RS), SH)

m

← MASK(MB, ME)

(RA) ← r ∧ m

The contents of register RS are rotated left by the number of bit positions specified in the SH field. A mask is gener-

ated, having 1-bits starting at the bit position specified in the MB field and ending in the bit position specified by the

ME field with 0-bits elsewhere.

If the starting point of the mask is at a higher bit position than the ending point, the 1-bits portion of the mask wraps

from the highest bit position back around to the lowest. The rotated data is ANDed with the generated mask; the

result is placed into register RA.

Registers Altered

•RA

• CR[CR0]

LT, GT, EQ, SO

if Rc contains 1

Architecture Note

This instruction is part of the PowerPC User Instruction Set Architecture.

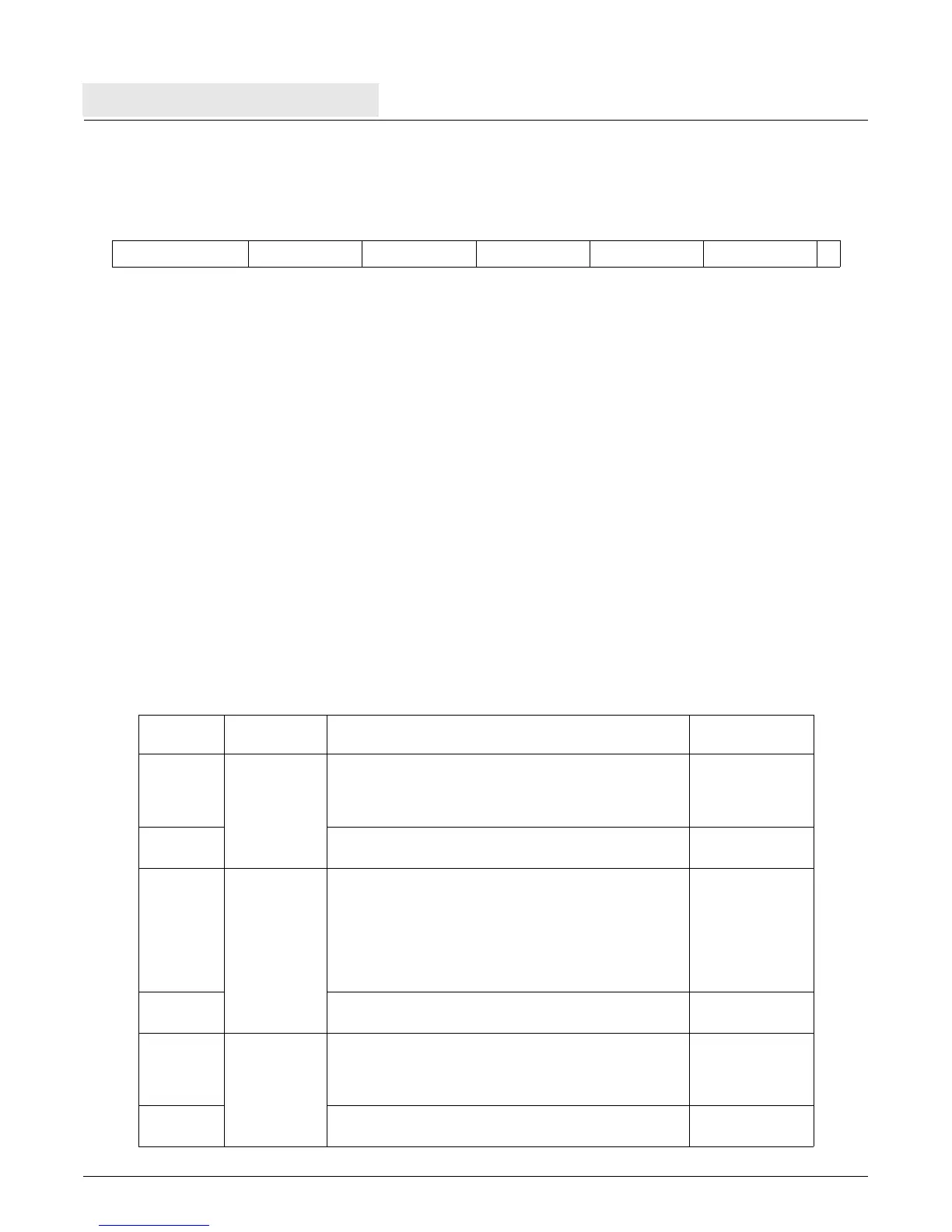

rlwinm RA, RS, SH, MB, ME Rc=0

rlwinm. RA, RS, SH, MB, ME Rc=1

21 RS RA SH MB ME Rc

0 6 11 16 21 26 31

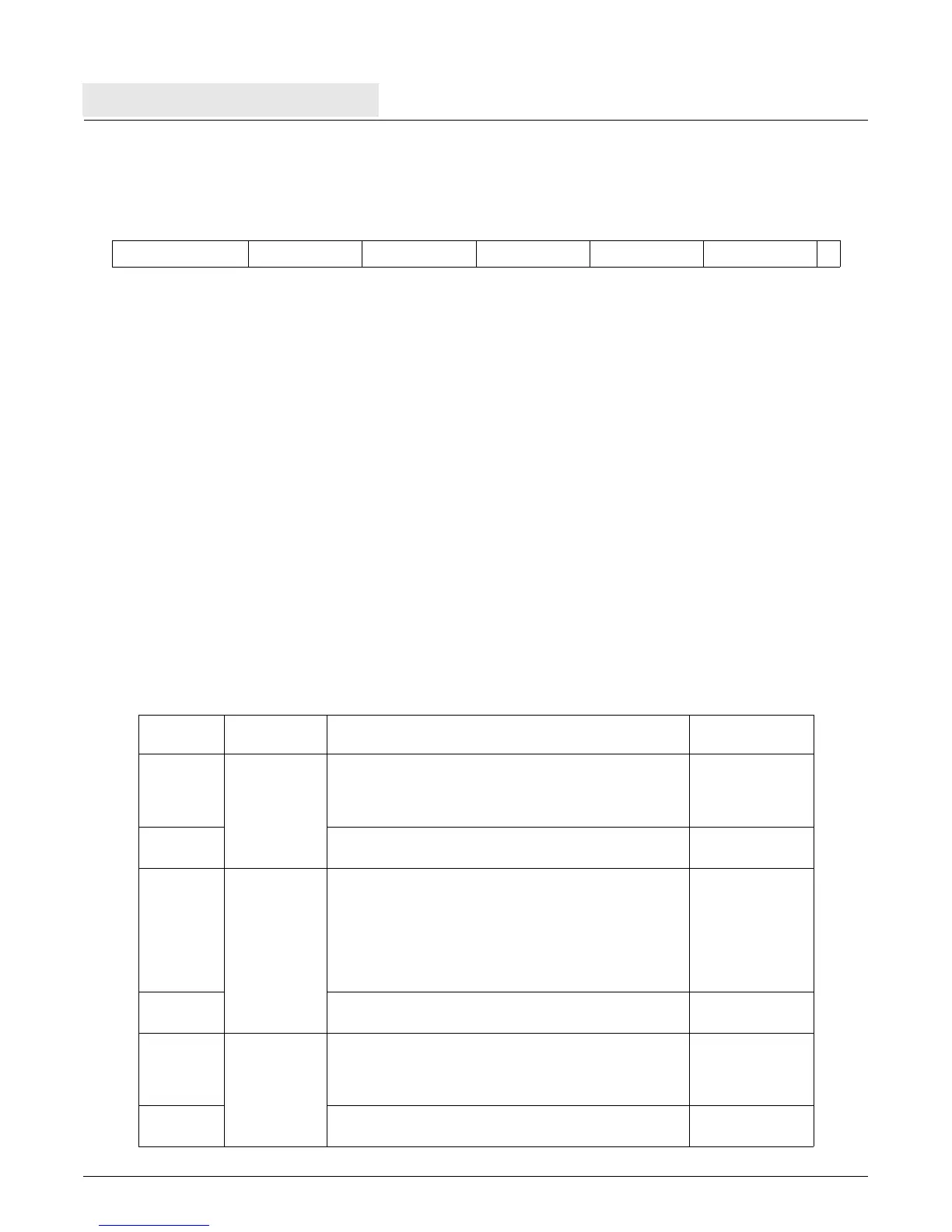

Table 9-28. Extended Mnemonics for rlwinm, rlwinm.

Mnemonic Operands Function

Other Registers

Altered

clrlwi

RA, RS, n

Clear left immediate. (

n < 32)

(RA)

0:n-1

←

n

0

Extended mnemonic for

rlwinm RA,RS,0,n,31

clrlwi.

Extended mnemonic for

rlwinm. RA,RS,0,n,31

CR[CR0]

clrlslwi

RA, RS, b, n

Clear left and shift left immediate.

(

n ≤ b < 32)

(RA)

b-n:31-n

← (RS)

b:31

(RA)

32-n:31

←

n

0

(RA)

0:b-n-1

←

b-n

0

Extended mnemonic for

rlwinm RA,RS,n,b−n,31−n

clrlslwi.

Extended mnemonic for

rlwinm. RA,RS,n,b−n,31−n

CR[CR0]

clrrwi

RA, RS, n

Clear right immediate. (

n < 32)

(RA)

32-n:31

←

n

0

Extended mnemonic for

rlwinm RA,RS,0,0,31−n

clrrwi.

Extended mnemonic for

rlwinm. RA,RS,0,0,31−n

CR[CR0]

Loading...

Loading...