152 AMCC Proprietary

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

The DAC Compare Size fields (DBCR1[D1S, D2S]) are not used by DAC range comparisons.

8.8.13.3 DAC Applied to Cache Instructions

Some cache instructions can cause DAC debug events. There are several special cases.

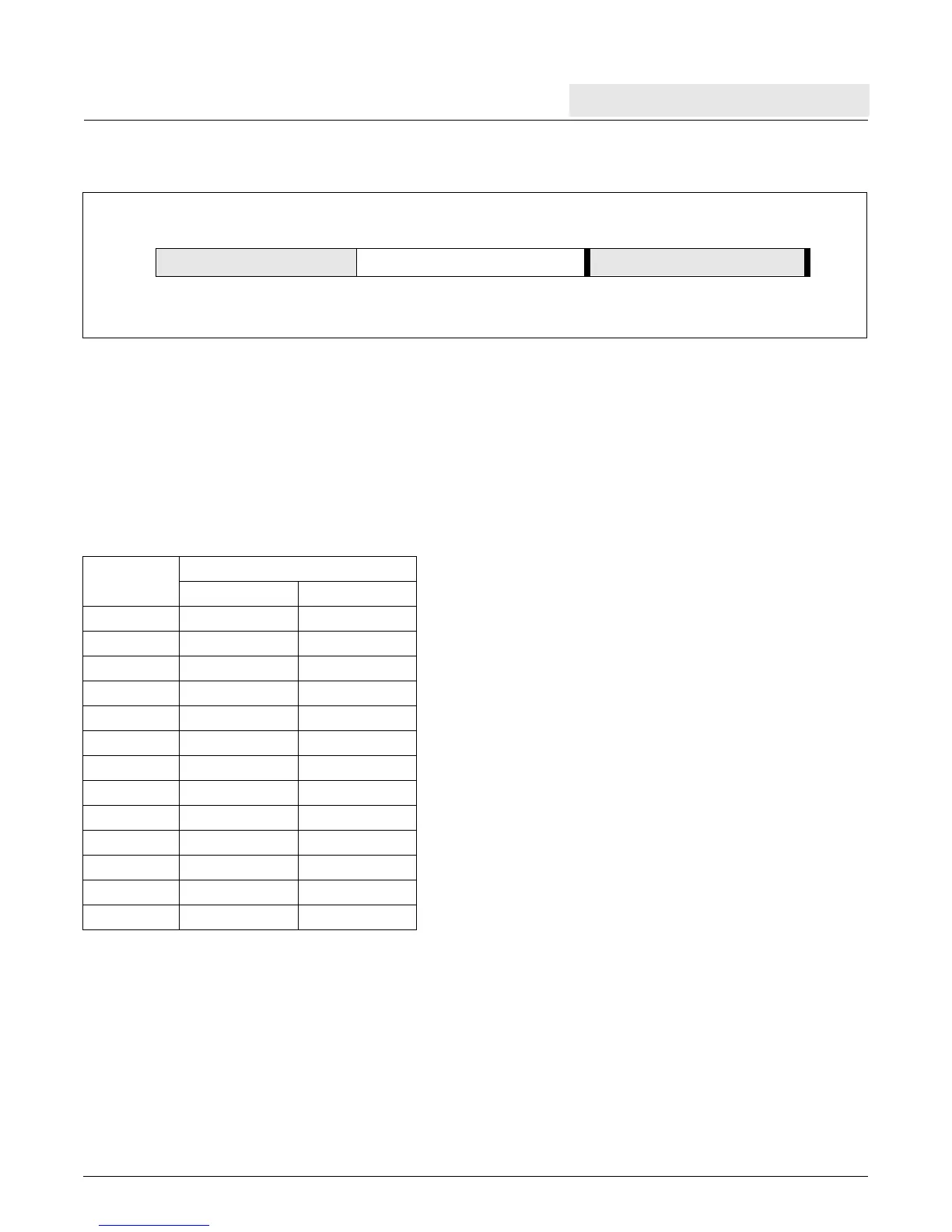

Table 8-3 summarizes possible DAC debug events by cache instruction:

Architecturally, the

dcbi and dcbz instructions are “stores.” These instructions can change data, or cause the loss

of data by invalidating a dirty line. Therefore, they can cause DAC-write debug events.

The

dccci instruction can also be considered a “store” because it can change data by invalidating a dirty line.

However,

dccci is not address-specific; it affects an entire congruence class regardless of the operand address of

the instruction. Because it is not address-specific, dccci does not cause DAC-write debug events.

Architecturally, the dcbt,

dcbtst, dcbf, and dcbst instructions are “loads.” These instructions do not change data.

Flushing or storing a cache line from the cache is not architecturally a “store” because a store had already updated

the cache; the

dcbf or dcbst instruction only updates the copy in main memory.

Figure 8-10. Exclusive DAC Range Address Compares

Table 8-3. DAC Applied to Cache Instructions

Instruction

Possible DAC Debug Event

DAC-Read DAC-Write

dcba No Yes

dcbf No Yes

dcbi No Yes

dcbst No Yes

dcbt Yes No

dcbz No Yes

dccci No No

dcread No No

dcbtst Yes No

icbi Yes No

icbt Yes No

iccci No No

icread No No

DAC1 DAC2

0

FFFF FFFF

Loading...

Loading...