AMCC Proprietary 57

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

2.9.3 Privileged SPRs

Most SPRs are privileged. The only defined non privileged SPRs are the LR, CTR, XER, USPRG0, and SPRG4–7

(read access only), TBU (read access only), and TBL (read access only). These registers are read using the mftb

instruction, rather than the mfspr instruction. TBL and TBU are written (with different addresses) using mtspr,

which is privileged for these registers. Except for moves to and from non privileged SPRs, attempts to execute

mfspr and mtspr instructions while in user mode result in privileged violation program exceptions.

In a mfspr or mtspr instruction, the 10-bit SPRN field specifies the SPR number of the source or destination SPR.

The SPRN field contains two five-bit subfields, SPRN0:4 and SPRN5:9. The assembler handles the unusual

register number encoding to generate the SPRF field. In the machine code for the mfspr and mtspr instructions,

the SPRN subfields are reversed (ending up as SPRF5:9 and SPRF0:4) for compatibility with the POWER

Architecture.

In the PowerPC Architecture, SPR numbers having a 1 in the most-significant bit of the SPRF field are privileged.

The following example illustrates how SPR numbers appear in assembler language coding and in machine coding

of the mfspr and mtspr instructions.

In assembler language coding, SRR0 is SPR 26. Note that the assembler handles the unusual register number

encoding to generate the SPRF field.

mfspr r5,26

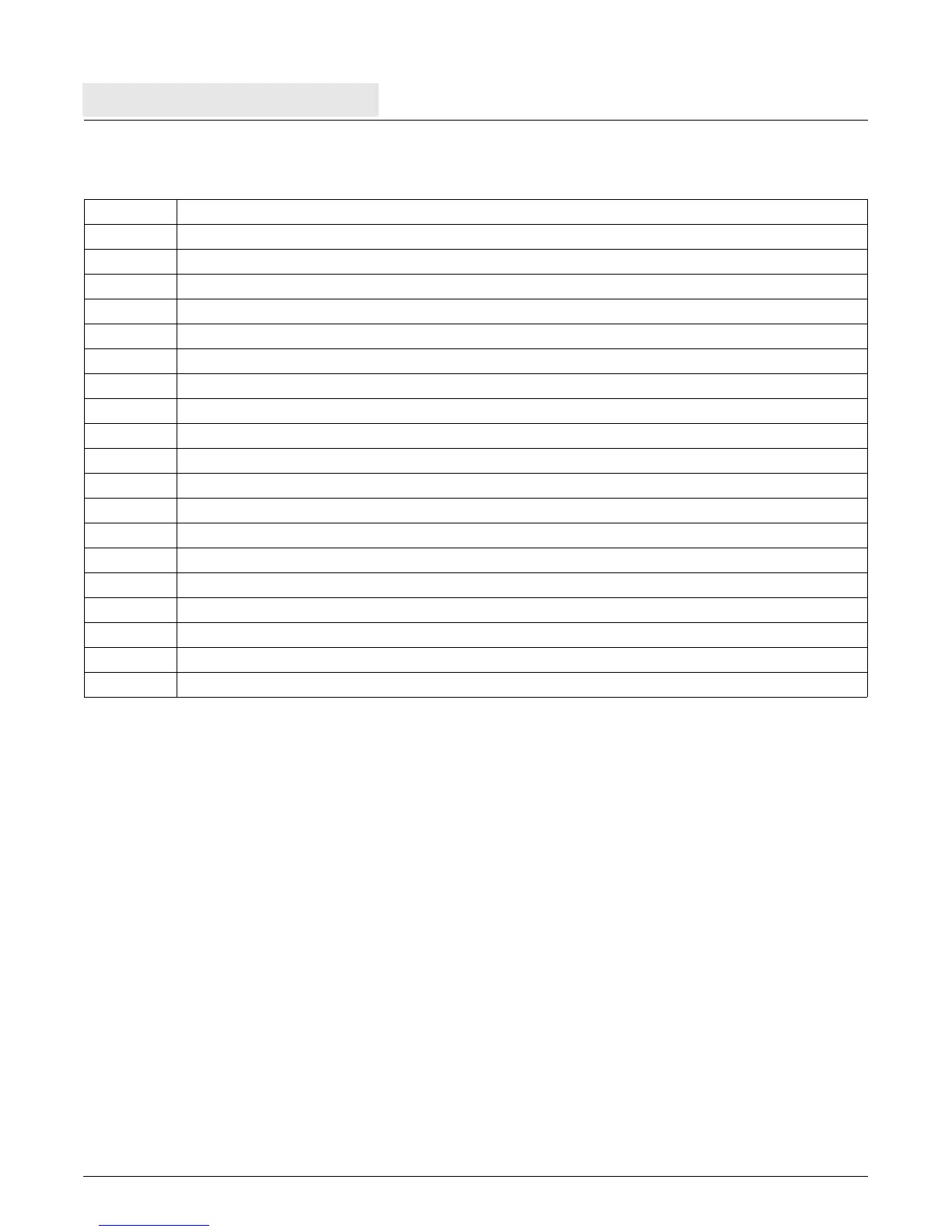

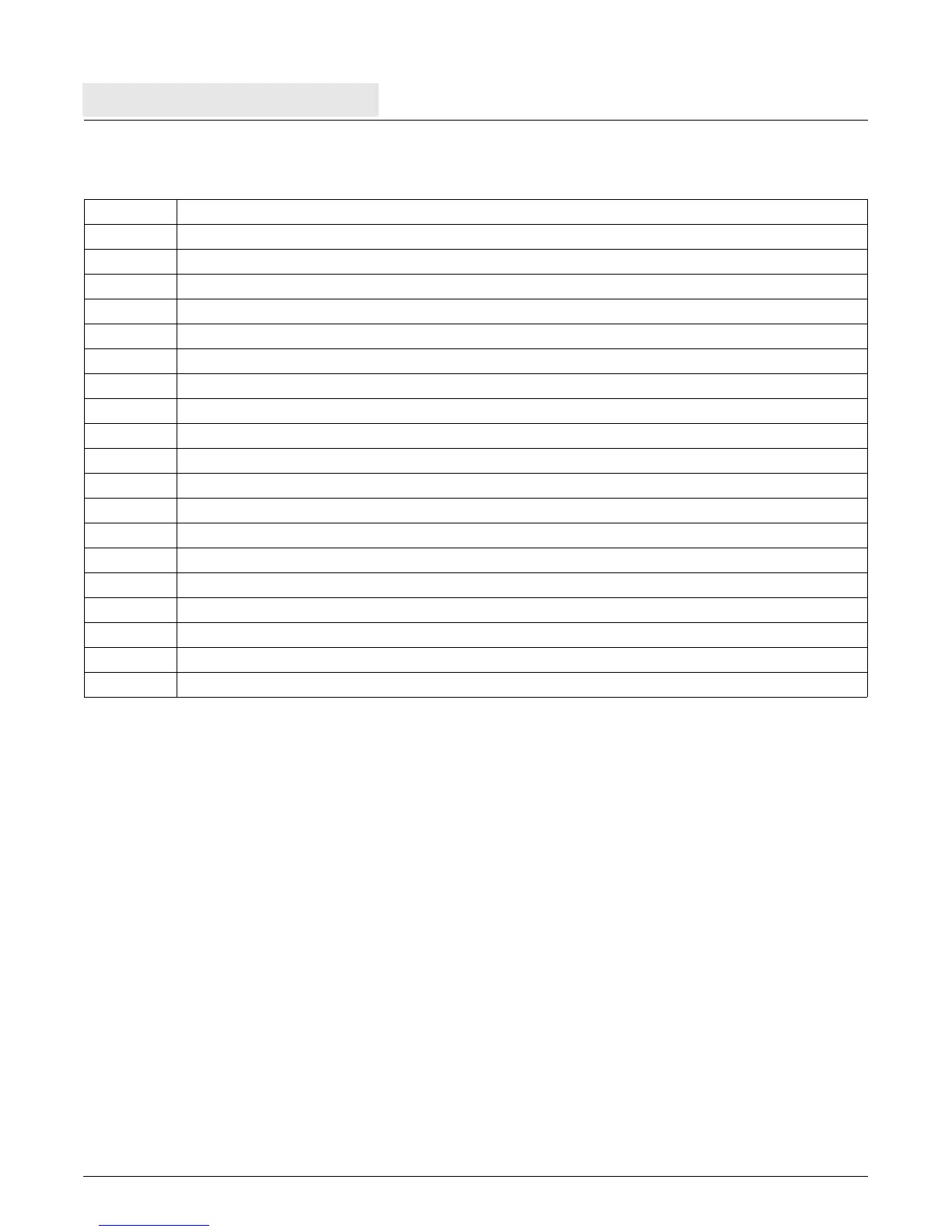

Table 2-11. Privileged Instructions

dcbi

dccci

dcread

iccci

icread

mfdcr

mfmsr

mfspr

For all SPRs except CTR, LR, SPRG4–SPRG7, and XER. See “Privileged SPRs” on page 57

mtdcr

mtmsr

mtspr

For all SPRs except CTR, LR, XER. See “Privileged SPRs” on page 57

rfci

rfi

tlbia

tlbre

tlbsx

tlbsync

tlbwe

wrtee

wrteei

Loading...

Loading...