148 AMCC Proprietary

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

In internal debug mode, the processor generates a debug interrupt when a debug event occurs. In external debug

mode, the processor stops when a debug event occurs. When internal and external debug mode are both enabled,

the processor stops on a debug event with the debug interrupt pending. When external and internal debug mode

are both disabled, and debug wait mode is enabled the processor stops, but can be restarted by an interrupt. When

all debug modes are disabled, debug events are recorded in the DBSR, but no action is taken.

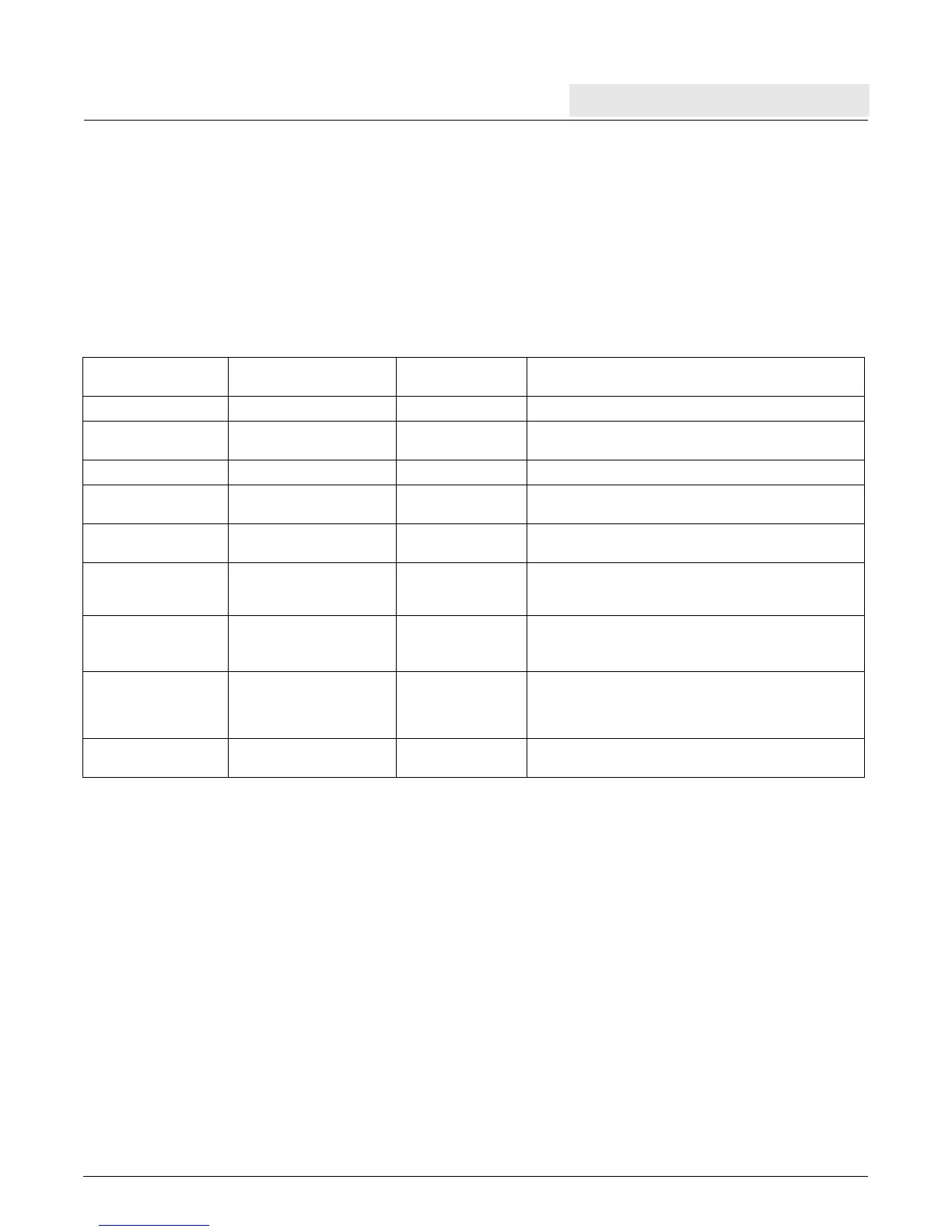

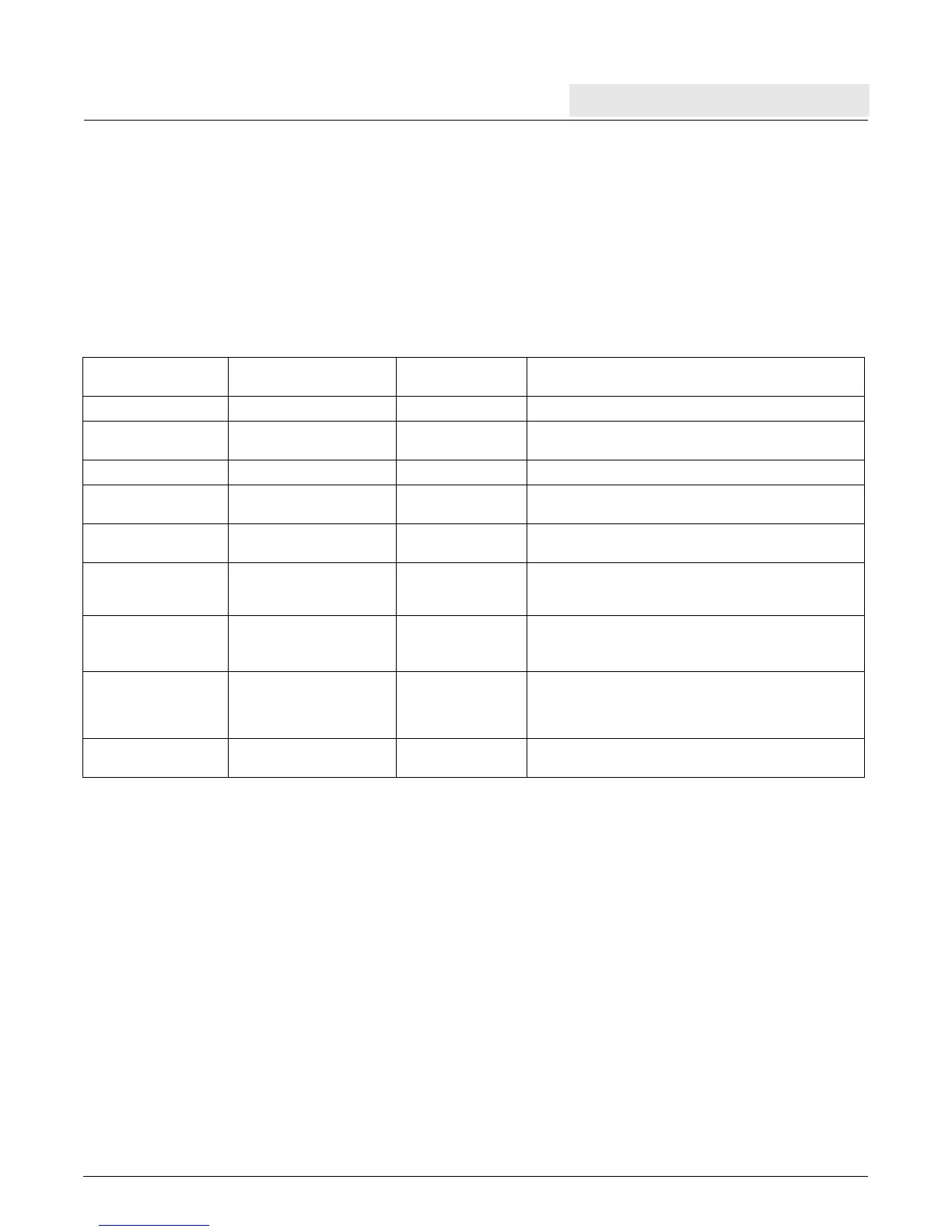

Table 8-2 lists the debug events and the related fields in DBCR0, DBCR1, and DBSR. DBCR0 and DBCR1 enable

the debugs events, and the DBSR fields report their occurrence.

8.8.7 Instruction Complete Debug Event

This debug event occurs after the completion of an instruction. If DBCR0[IDM] = 1, DBCR0[EDM] = 0 and

MSR[DE] =0 this debug event is disabled.

8.8.8 Branch Taken Debug Event

This debug event occurs before execution of a branch instruction determined to be taken. If DBCR0[IDM] = 1,

DBCR0[EDM] = 0 and MSR[DE] =0 this debug event is disabled.

8.8.9 Exception Taken Debug Event

This debug event occurs after an exception. Exception debug events always include the non-critical class of

exceptions. When DBCR0[IDM] = 1 and DBCR0[EDM] = 0 the critical exceptions are not included.

Table 8-2. Debug Events

Event

Enabling

DBCR0, DBCR1 Fields

Reporting

DBSR Fields

Description

Instruction Completion IC IC Occurs after completion of an instruction.

Branch Taken BT BT

Occurs before execution of a branch instruction deter-

mined to be taken.

Exception Taken EDE EXC Occurs after an exception.

Trap Instruction TDE TIE

Occurs before execution of a trap instruction where the

conditions are such that the trap will occur.

Unconditional UDE UDE

Occurs immediately upon being set by the JTAG debug

port.

Instruction Address

Compare

IA1, IA2, IA3, IA4, IA12,

IA12X, IA12T, IA34,

IA34X, IA34T

IA1, IA2, IA3, IA4

Occurs before execution of an instruction at an address

that matches an address defined by the Instruction

Address Compare Registers (IAC1–IAC4).

Data Address Com-

pare

D1R, D1W, D1S, D2R,

D2W, D2S,

DA12, DA12X

DR2,DW2

Occurs before execution of an instruction that accesses a

data address that matches the contents of the specified

DAC register.

Data Value Compare

DV1M, DV2M, DV1BE,

DV2BE

DR1, DW1

Occurs after execution of an instruction that accesses a

data address for which a DAC occurs, and for which the

value at the address matches the value in the specified

DVC register.

Imprecise IDE

Indicates that another debug event occurred while

MSR[DE] = 0

Loading...

Loading...