AMCC Proprietary 117

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

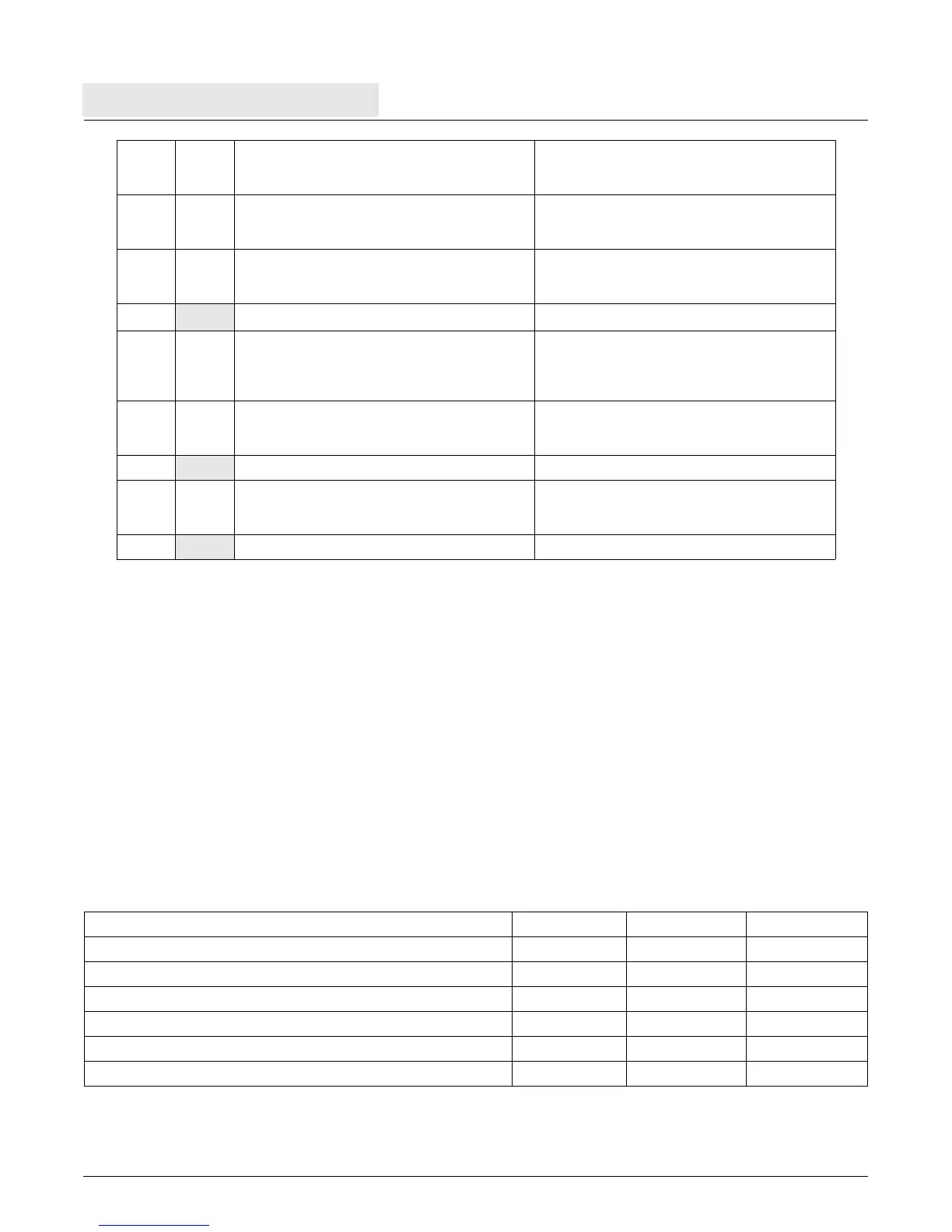

In general, ESR bits are set to indicate the type of precise interrupt that occurred; other bits are cleared. However,

the machine check—instruction (ESR[MCI]) bit behaves differently. Because instruction-side machine checks can

occur without an interrupt being taken (if MSR[ME] = 0), ESR[MCI] can be set even while other ESR-setting

interrupts (program, data storage, DTLB-miss) occurring. Thus, data storage and program interrupts leave

ESR[MCI] unchanged, clear all other ESR bits, and set the bits associated with any data storage or program

interrupts that occurred. Enabled instruction-side machine checks (MSR[ME] = 1) set ESR[MCI] and clear the data

storage and program interrupt bits.

If a machine check—instruction interrupt occurs but is disabled (MSR[ME] = 0), it sets but leaves the data storage

and program interrupt bits alone. If a machine check—instruction interrupt occurs while MSR[ME] = 0, and the

instruction upon which the machine check—instruction interrupt is occurring also is some other kind of ESR-setting

instruction (program, data storage, DTLB-miss, or instruction storage interrupt), ESR[MCI] is set to indicate that a

machine check—instruction interrupt occurred; the other ESR bits are set or cleared to indicate the other interrupt.

These scenarios are summarized in Table 6-3.

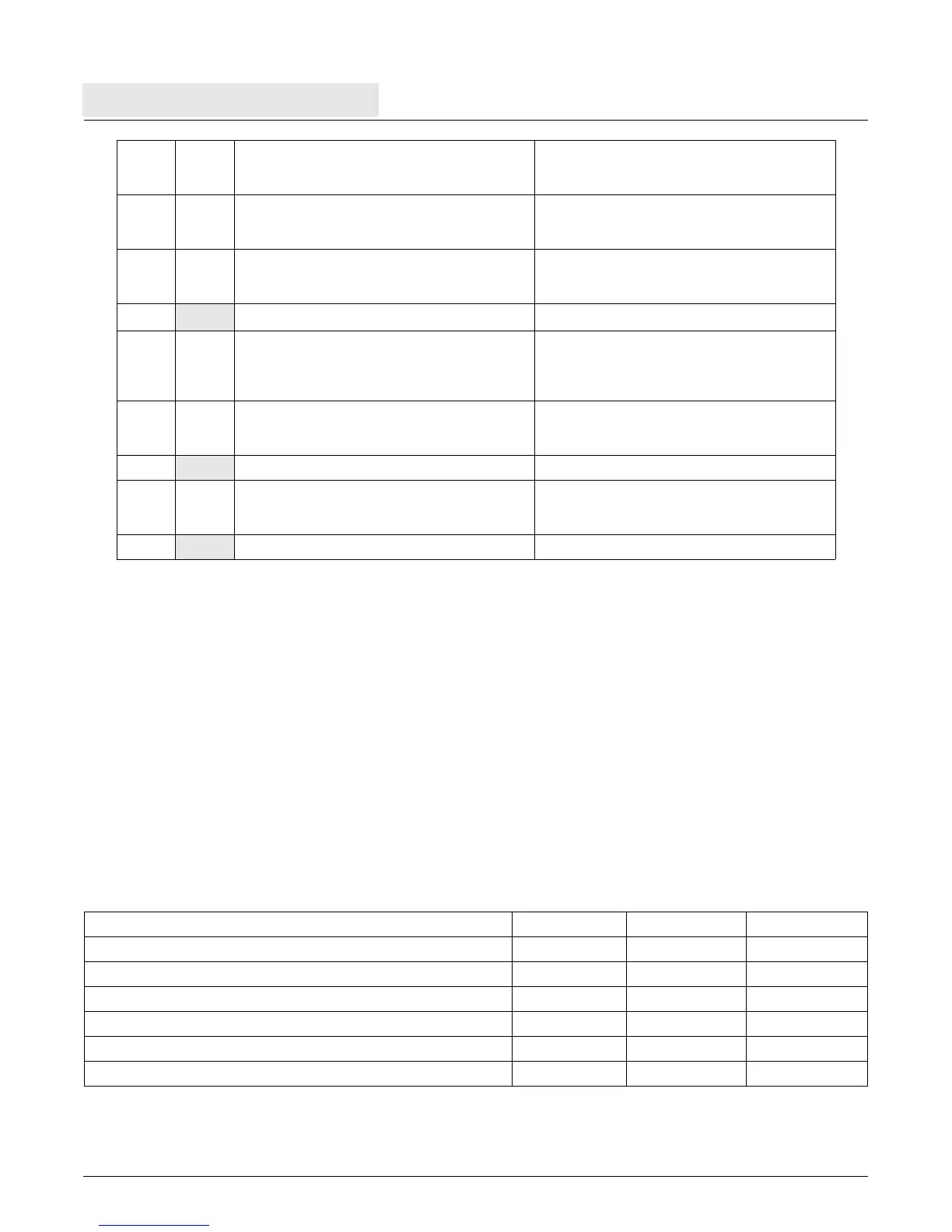

4 PIL Program interrupt—illegal

0 Illegal Instruction error did not occur.

1 Illegal Instruction error occurred.

5 PPR Program interrupt—privileged

0 Privileged instruction error did not occur.

1 Privileged instruction error occurred.

6 PTR Program interrupt—trap

0 Trap with successful compare did not occur.

1 Trap with successful compare occurred.

7

Reserved

8 DST Data storage interrupt—store fault

0 Excepting instruction was not a store.

1 Excepting instruction was a store (includes dcbi,

dcbz, and dccci).

9 DIZ Data/instruction storage interrupt—zone fault

0 Excepting condition was not a zone fault.

1 Excepting condition was a zone fault.

10:15

Reserved

16 U0F Data storage interrupt—U0 fault

0 Excepting instruction did not cause a U0 fault.

1 Excepting instruction did cause a U0 fault.

17:31

Reserved

Table 6-3. ESR Alteration by Various Interrupts

Scenario ECR[MCI] ESR

4:

ESR

8:9, 16

Program interrupt Unchanged Set to type Cleared

Data storage interrupt Unchanged Cleared Set to Type

Data TLB miss interrupt Unchanged Cleared Cleared

Machine check—instruction Set to 1 Cleared Cleared

Disabled MCI, no others Unchanged Unchanged Unchanged

Disabled MCI and program interrupt Unchanged Set to type Cleared

Loading...

Loading...