AMCC Proprietary 395

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

Appendix B. Instructions by Category

Instruction Set on page 157 contains detailed descriptions of the instructions, their operands, and notation.

Table B-1 summarizes the instruction categories in the PPC405 instruction set. The instructions within each

category are listed in subsequent tables.

B.1 Implementation-Specific Instructions

To meet the functional requirements of processors for embedded systems and real-time applications, the PPC405

defines the implementation-specific instructions summarized in Table B-2.

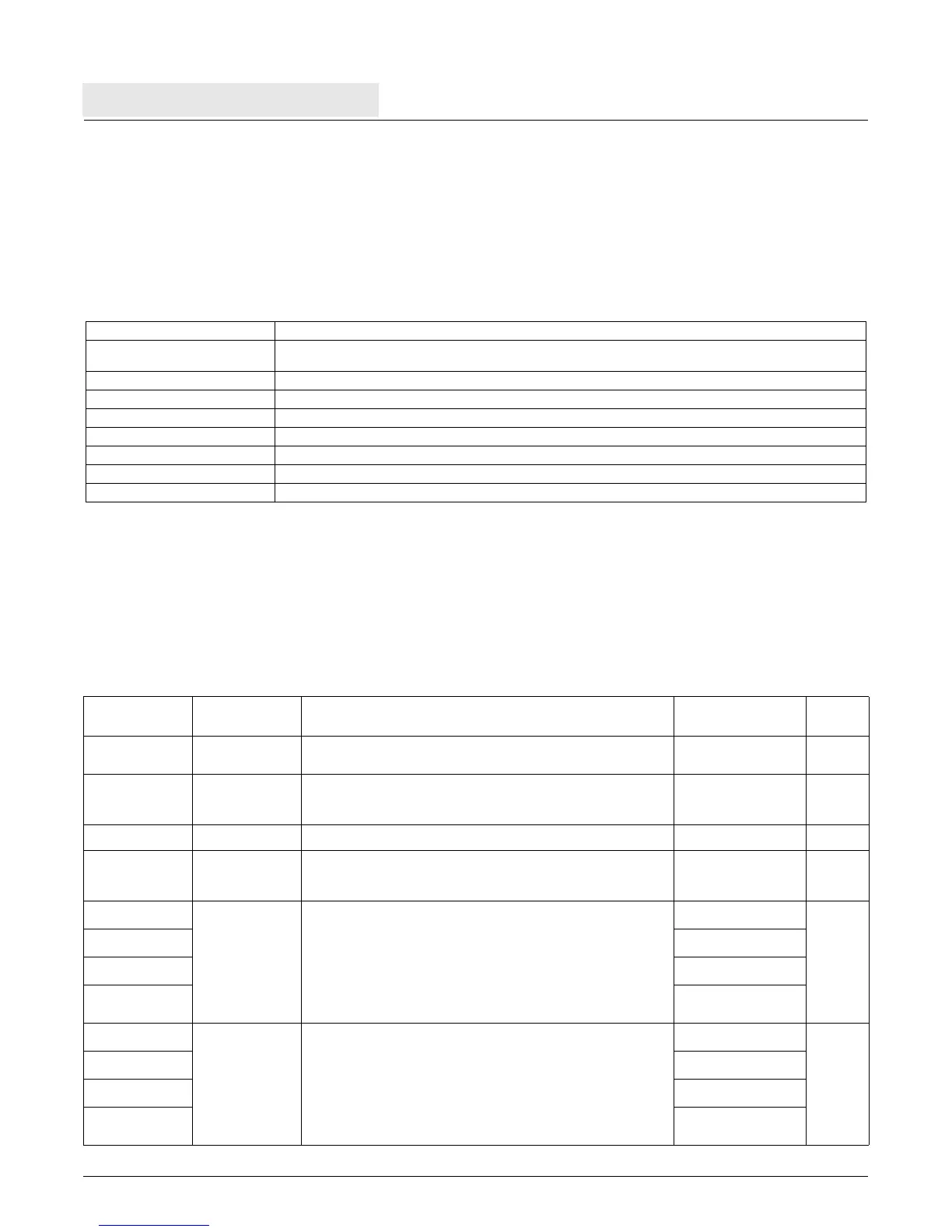

Table B-1. PPC405 Instruction Set Categories

Storage Reference load, store

Arithmetic and Logical add, subtract, negate, multiply, divide, and, andc, or, orc, xor, nand, nor, xnor, sign extension, count

leading zeros, multiply accumulate

Comparison compare, compare logical, compare immediate

Branch branch, branch conditional, branch to LR, branch to CTR

CR Logical crand, crandc, cror, crorc, crnand, crnor, crxor, crxnor, move CR field

Rotate/Shift rotate and insert, rotate and mask, shift left, shift right

Cache Control invalidate, touch, zero, flush, store, read

Interrupt Control write to external interrupt enable bit, move to/from MSR, return from interrupt, return from critical interrupt

Processor Management system call, synchronize, trap, move to/from DCRs, move to/from SPRs, move to/from CR

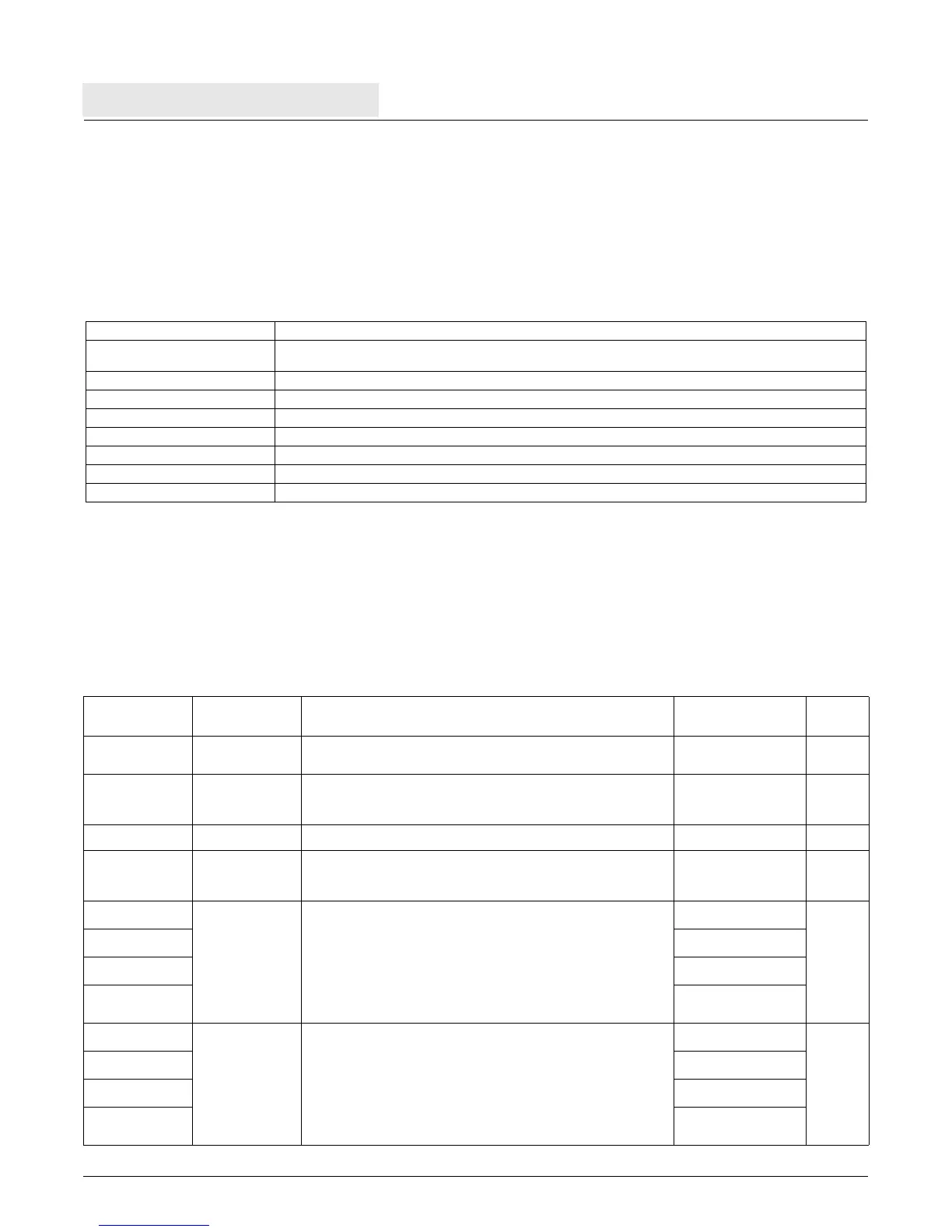

Table B-2. Implementation-specific Instructions

Mnemonic Operands Function

Other Registers

Changed

Page

dccci RA, RB Invalidate the data cache congruence class associated with the

effective address (EA) (RA|0) + (RB).

210

dcread RT, RA, RB Read either tag or data information from the data cache

congruence class associated with the EA (RA|0) + (RB).

Place the results in RT.

211

iccci RA, RB Invalidate instruction cache. 221

icread RA, RB Read either tag or data information from the instruction cache

congruence class associated with the EA (RA|0) + (RB).

Place the results in ICDBDR.

222

macchw

RT, RA, RB prod

0:31

← (RA)

16:31

x (RB)

0:15

signed

temp

0:32

← prod

0:31

+ (RT)

(RT)

← temp

1:32

222

macchw.

CR[CR0]

macchwo

XER[SO, OV]

macchwo.

CR[CR0]

XER[SO, OV]

macchws

RT, RA, RB prod

0:31

← (RA)

16:31

x (RB)

0:15

signed

temp

0:32

← prod

0:31

+ (RT)

if ((prod

0

= RT

0

) ∧ (RT

0

≠ temp

1

)) then

(RT)

← (RT

0

||

31

(¬RT

0

))

else (RT)

← temp

1:32

250

macchws.

CR[CR0]

macchwso

XER[SO, OV]

macchwso.

CR[CR0]

XER[SO, OV]

Loading...

Loading...