AMCC Proprietary 427

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

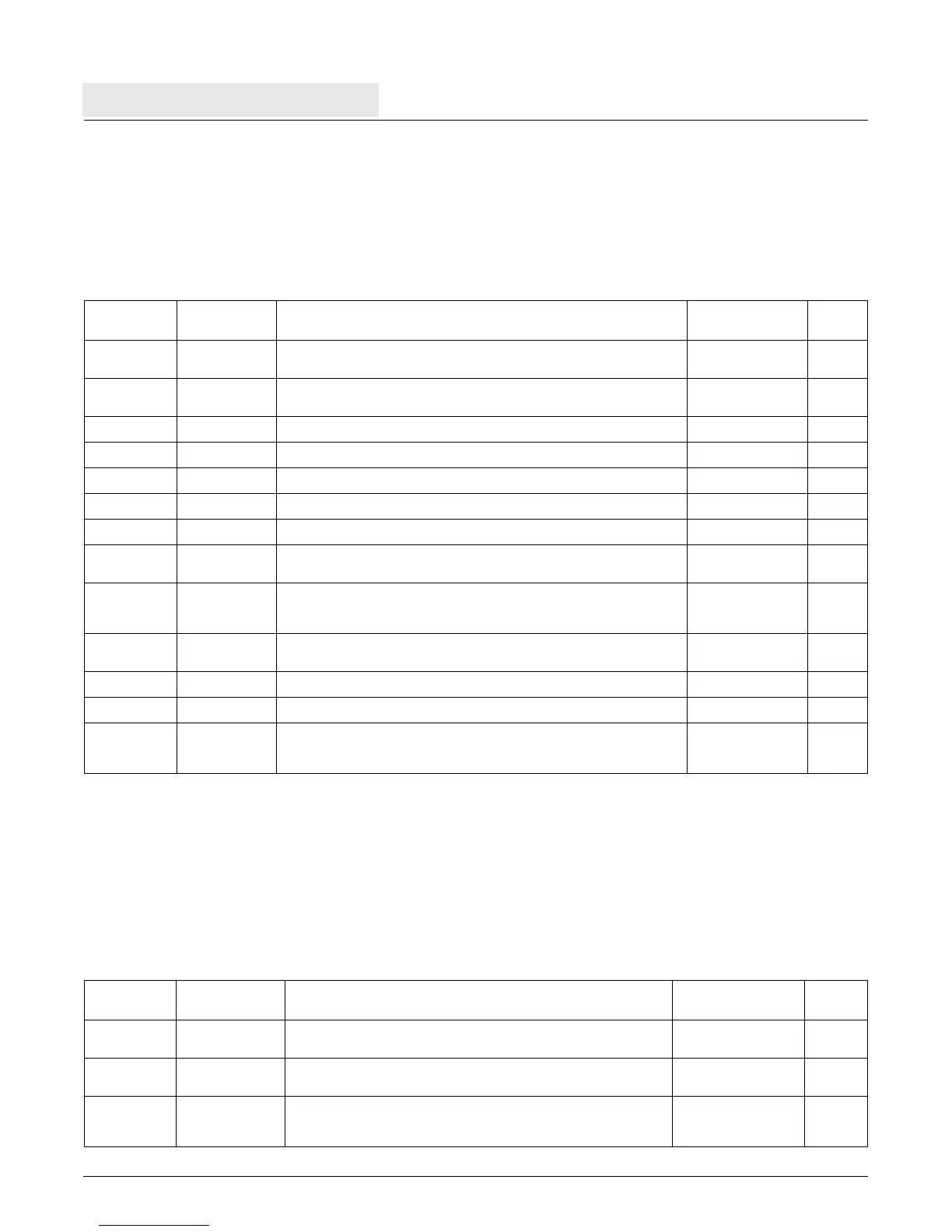

B.11 Cache Control Instructions

Cache control instructions allow the user to indirectly control the contents of the data and instruction caches. The

user may fill, flush, invalidate and zero blocks (16-byte lines) in the data cache. The user may also invalidate

congruence classes in both caches and invalidate individual lines in the instruction cache.

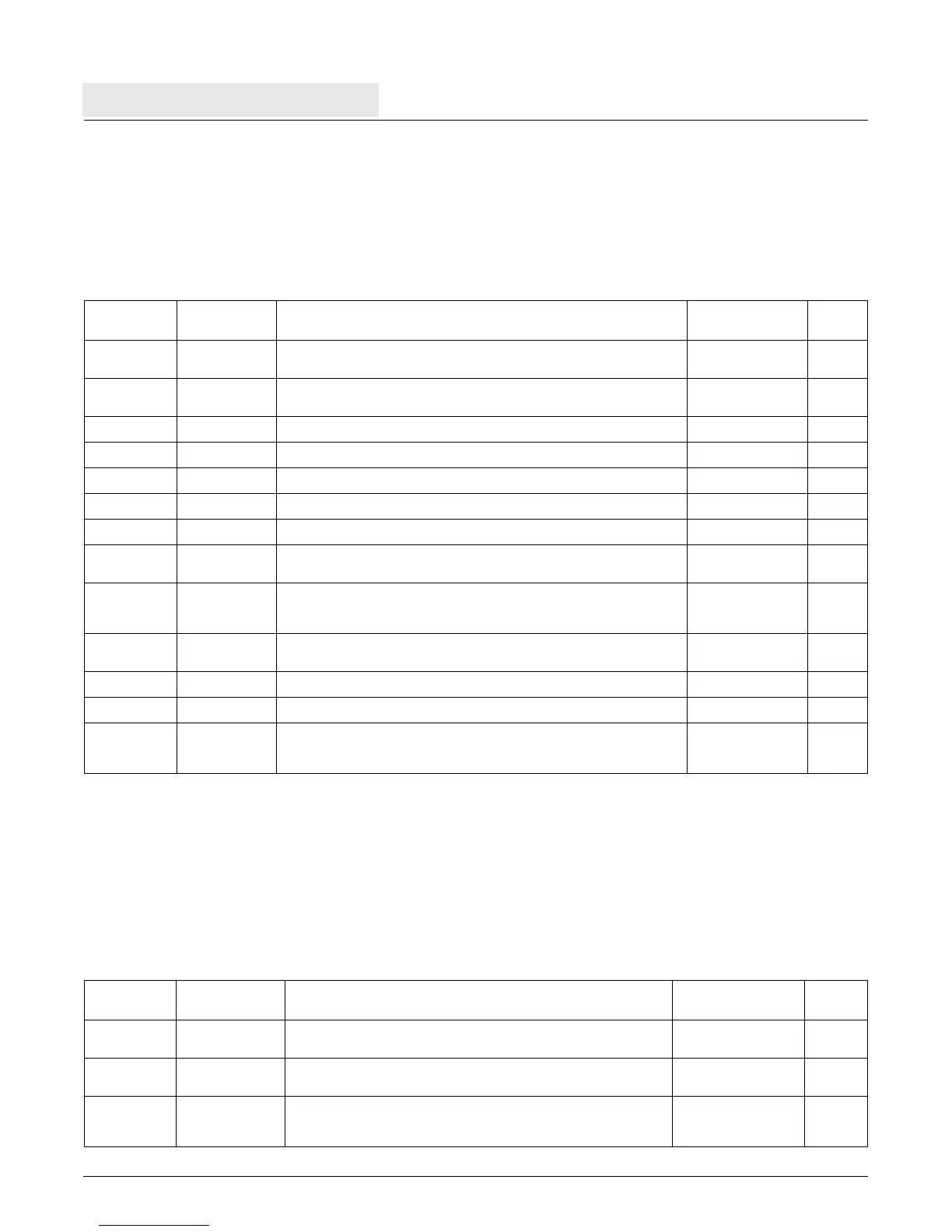

B.12 Interrupt Control Instructions

The interrupt control instructions allow the user to move data between general purpose registers and the machine

state register, return from interrupts and enable or disable maskable external interrupts. Table B-13 shows the

interrupt control instruction set.

Table B-12. Cache Control Instructions

Mnemonic Operands Function

Other Registers

Changed

Page

dcba RA, RB Speculatively establish the data cache block which contains the EA

(RA|0) + (RB).

201

dcbf RA, RB Flush (store, then invalidate) the data cache block which contains the EA

(RA|0) + (RB).

203

dcbi RA, RB Invalidate the data cache block which contains the EA (RA|0) + (RB). 204

dcbst RA, RB Store the data cache block which contains the EA (RA|0) + (RB). 205

dcbt RA, RB Load the data cache block which contains the EA (RA|0) + (RB). 206

dcbtst RA,RB Load the data cache block which contains the EA (RA|0) + (RB). 207

dcbz RA, RB Zero the data cache block which contains the EA (RA|0) + (RB). 208

dccci RA, RB Invalidate the data cache congruence class associated with the EA

(RA|0) + (RB).

210

dcread RT, RA, RB Read either tag or data information from the data cache congruence

class associated with the EA (RA|0) + (RB).

Place the results in RT.

211

icbi RA, RB Invalidate the instruction cache block which contains the EA

(RA|0) + (RB).

219

icbt RA, RB Load the instruction cache block which contains the EA (RA|0) + (RB). 220

iccci RA, RB Invalidate instruction cache. 221

icread RA, RB Read either tag or data information from the instruction cache

congruence class associated with the EA (RA|0) + (RB).

Place the results in ICDBDR.

221

Table B-13. Interrupt Control Instructions

Mnemonic Operands Function

Other Registers

Changed

Page

mfmsr RT Move from MSR to RT,

(RT)

← (MSR).

265

mtmsr RS Move to MSR from RS,

(MSR)

← (RS).

271

rfci Return from critical interrupt

(PC)

← (SRR2).

(MSR)

← (SRR3).

297

Loading...

Loading...