AMCC Proprietary 269

Revision 1.02 - September 10, 2007

PPC405 Processor

mtcrf

Move to Condition Register Fields

Preliminary User’s Manual

mtcrf

Move to Condition Register Fields

mask ←

4

(FXM

0

) ||

4

(FXM

1

) || ... ||

4

(FXM

6

) ||

4

(FXM

7

)

(CR)

← ((RS) ∧ mask) ∨ ((CR) ∧¬mask)

Some or all of the contents of register RS are placed into the CR as specified by the FXM field.

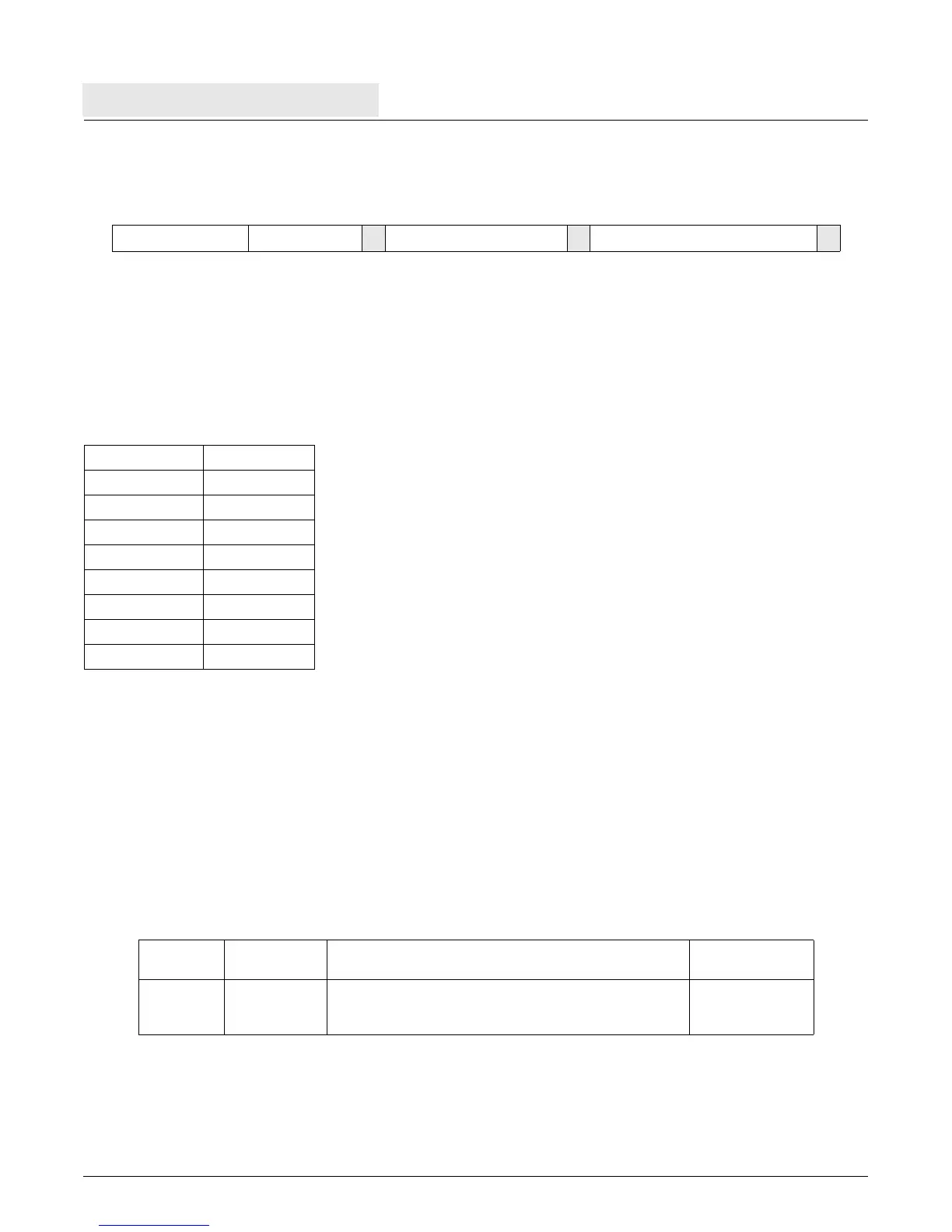

Each bit in the FXM field controls the copying of 4 bits in register RS into the corresponding bits in the CR. The

correspondence between the bits in the FXM field and the bit copying operation is shown in the following table:

If instruction bit 31 contains 1, the contents of CR[CR0] are undefined.

Registers Altered

•CR

Invalid Instruction Forms

• Reserved fields

Architecture Note

This instruction is part of the PowerPC User Instruction Set Architecture.

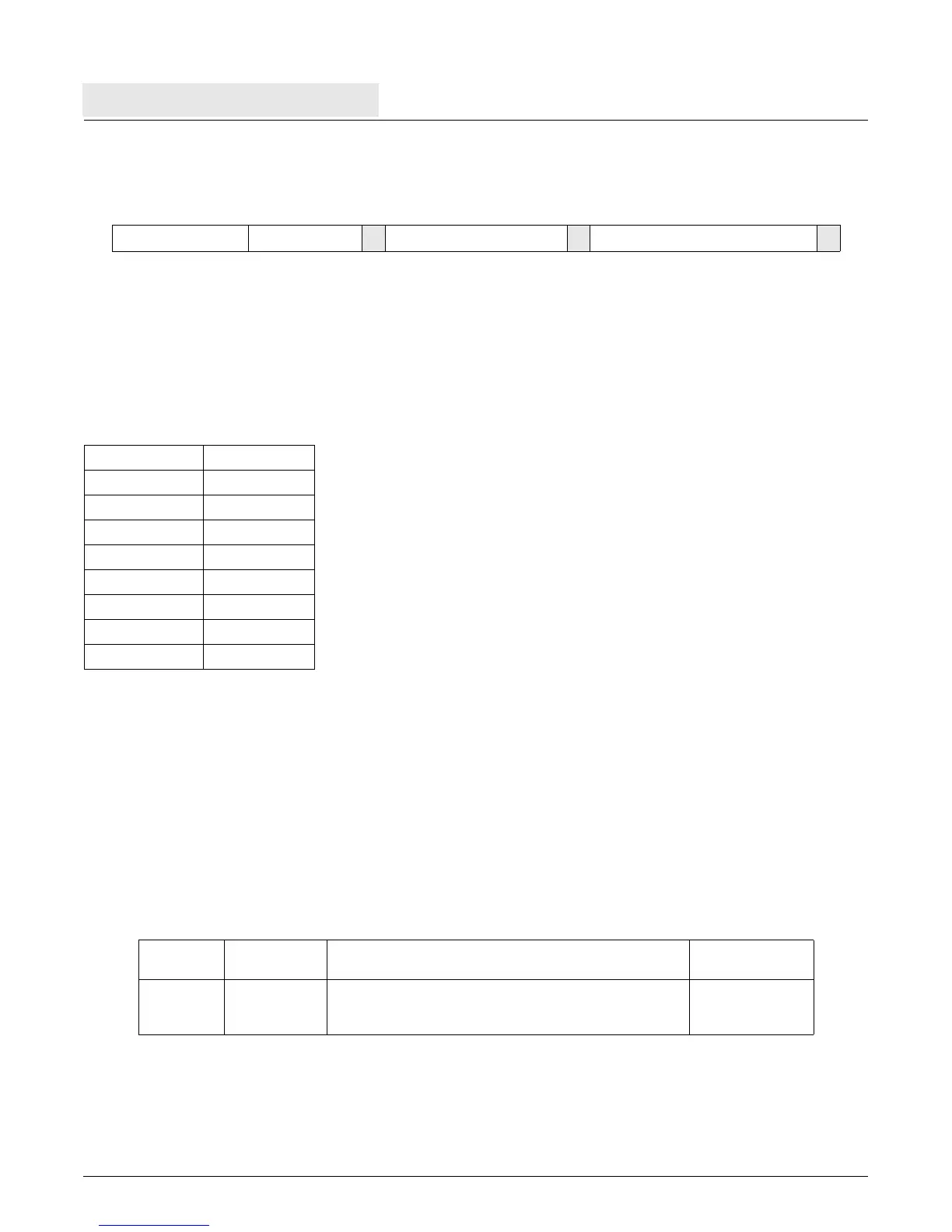

mtcrf FXM, RS

31 RS

FXM 144

0 6 11 12 20 21 31

FXM Bit Number Bits Controlled

00:3

14:7

28:11

3 12:15

4 16:19

5 20:23

6 24:27

7 28:31

Table 9-22. Extended Mnemonics for mtcrf

Mnemonic Operands Function

Other Registers

Altered

mtcr RS

Move to CR.

Extended mnemonic for

mtcrf 0xFF,RS

Loading...

Loading...