AMCC Proprietary 40

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

If a CR field is set by a compare instruction, the bits are set as described in the next section.

The CR is part of the user programming model.

2.3.3.1 CR Fields After Compare Instructions

Compare instructions compare the values of two 32-bit registers. The two types of compare instructions, arithmetic

and logical, are distinguished by the interpretation given to the 32-bit values. For arithmetic compares, the values

are considered to be signed, where 31 bits represent the magnitude and the most-significant bit is a sign bit. For

logical compares, the values are considered to be unsigned, so all 32 bits represent magnitude. There is no sign

bit. As an example, consider the comparison of 0 with 0xFFFFFFFF. In an arithmetic compare, 0 is larger, because

0xFFFF FFFF represents –1; in a logical compare, 0xFFFFFFFF is larger.

A compare instruction can direct its CR update to any CR field. The first data operand of a compare instruction

specifies a GPR. The second data operand specifies another GPR, or immediate data derived from the IM field of

the immediate instruction form. The contents of the GPR specified by the first data operand are compared with the

contents of the GPR specified by the second data operand (or with the immediate data). See descriptions of the

compare instructions (page 24-34 through page 24-37) for precise details.

2.3.3.2 The CR0 Field

After the execution of compare instructions that update CR[CR0], CR[CR0] is interpreted as described in “CR

Fields After Compare Instructions” on page 40. The “dot” forms of arithmetic and logical instructions also alter

CR[CR0]. After most instructions that update CR[CR0], the bits of CR0 are interpreted as follows:

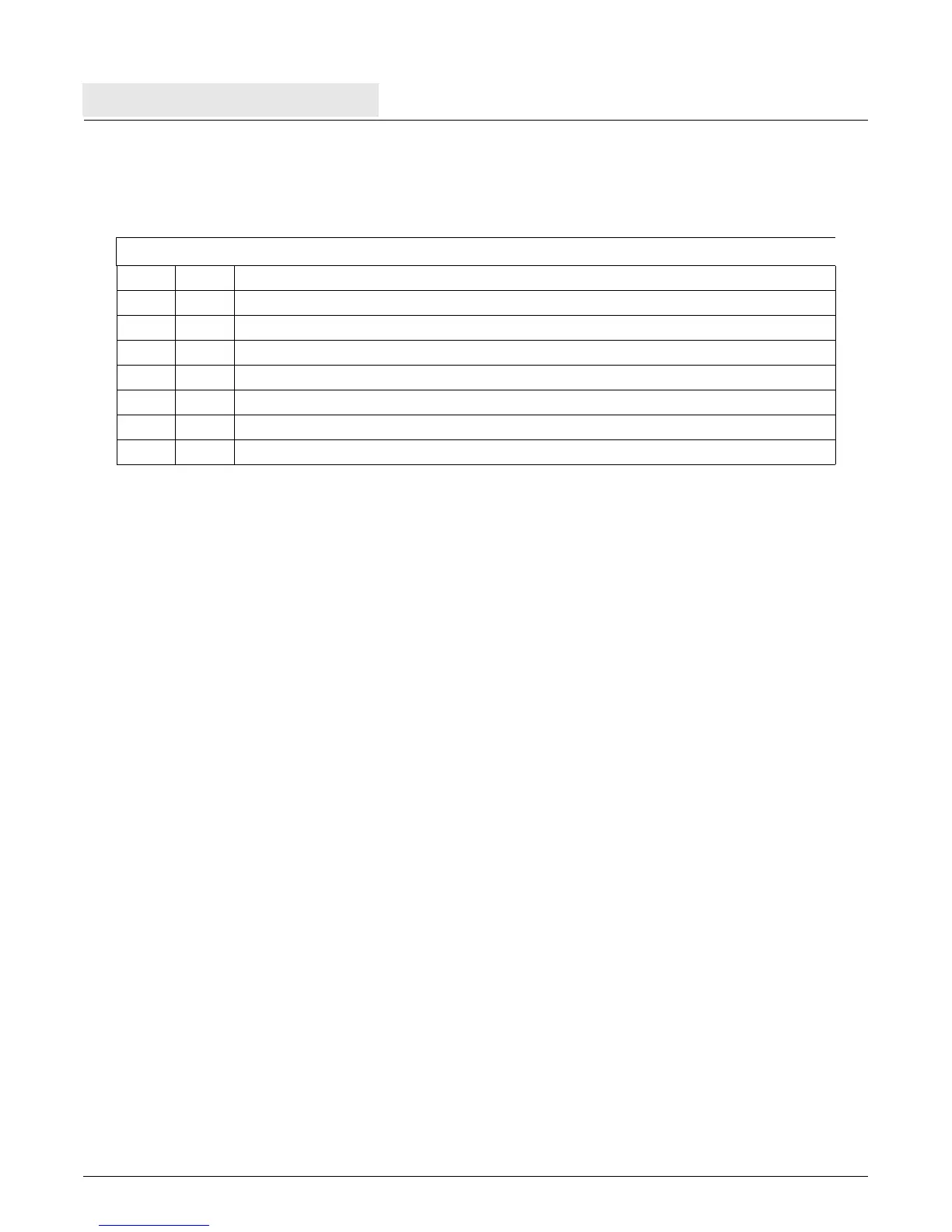

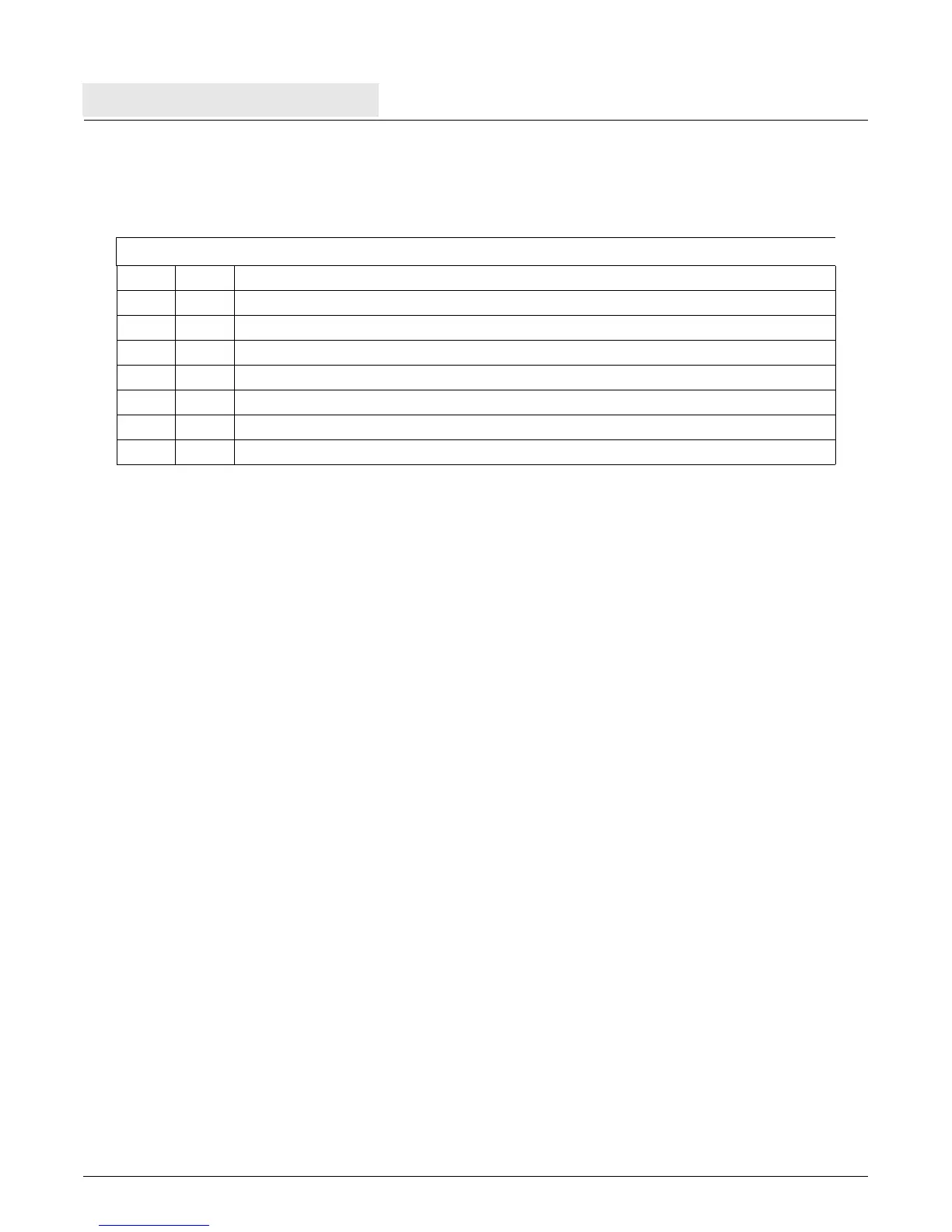

Figure 2-9. Condition Register (CR)

0:3 CR0 Condition Register Field 0

4:7 CR1 Condition Register Field 1

8:11 CR2 Condition Register Field 2

12:15 CR3 Condition Register Field 3

16:19 CR4 Condition Register Field 4

20:23 CR5 Condition Register Field 5

24:27 CR6 Condition Register Field 6

28:31 CR7 Condition Register Field 7

LT (bit 0) The first operand is less than the second operand.

GT (bit 1) The first operand is greater than the second operand.

EQ (bit 2) The first operand is equal to the second operand.

SO (bit 3) Summary overflow; a copy of XER[SO].

LT (bit 0) Less than 0; set if the most-significant bit of the 32-bit result is 1.

GT (bit 1)

Greater than 0; set if the 32-bit result is non-zero and the most-significant bit

of the result is 0.

EQ (bit 2) Equal to 0; set if the 32-bit result is 0.

SO (bit 3) Summary overflow; a copy of XER[SO] at instruction completion.

Loading...

Loading...