AMCC Proprietary 46

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

2.5.3 Endian (E) Storage Attribute

The endian (E) storage attribute supports direct connection of the PPC405 to little endian peripherals and to

memory containing little endian instructions and data. For every storage reference (instruction fetch or load/store

access), an E storage attribute is associated with the storage region of the reference. The E attribute specifies

whether that region is organized as big endian (E = 0) or little endian (E = 1).

When address translation is enabled (MSR[IR] = 1 or MSR[DR] = 1), the E field in the corresponding TLB entry

controls the endianness of a memory region. When address translation is disabled (MSR[IR] = 0 or MSR[DR] = 0),

the SLER controls the endianness of a memory region.

Bytes in storage that are accessed as little endian are arranged in true little endian format. The PPC405 does not

support the little endian mode defined in the PowerPC architecture and used in PPC401xx and PPC403xx

processors. Furthermore, no address modification is performed when accessing storage regions programmed as

little endian. Instead, the PPC405 reorders the bytes as they are transferred between the processor and memory.

The on-the-fly reversal of bytes in little endian storage regions is handled in one of two ways, depending on

whether the storage access is an instruction fetch or a data access (load/store). The following sections describe

byte reordering for the two kinds of storage accesses.

2.5.3.1 Fetching Instructions from Little Endian Storage Regions

Instructions are words (four bytes) that are aligned on word boundaries in memory. As such, instructions in a big

endian memory region are arranged with the most significant byte (MSB) of the instruction word at the lowest

address.

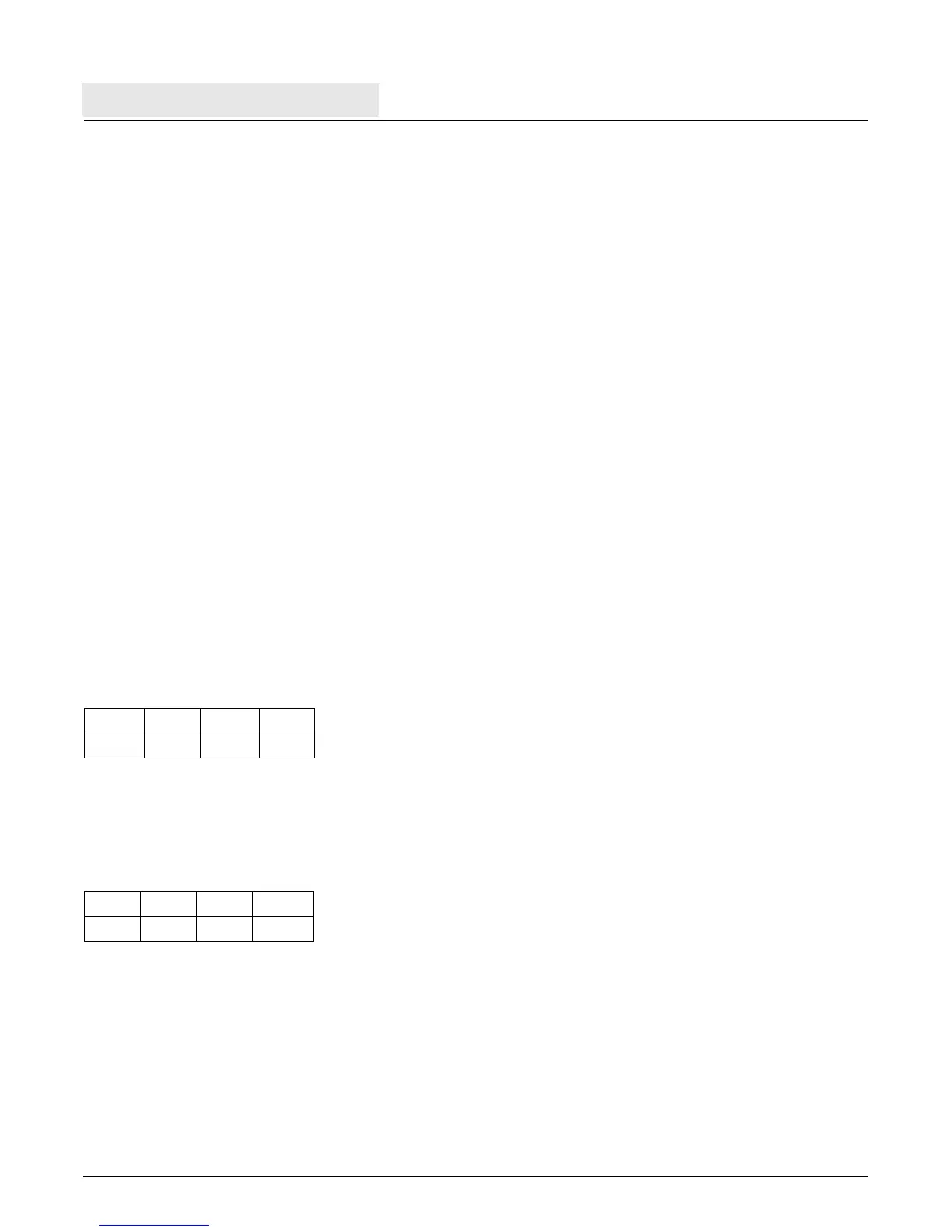

Consider the big endian mapping of instruction p at address 00, where, for example, p = add r7, r7, r4:

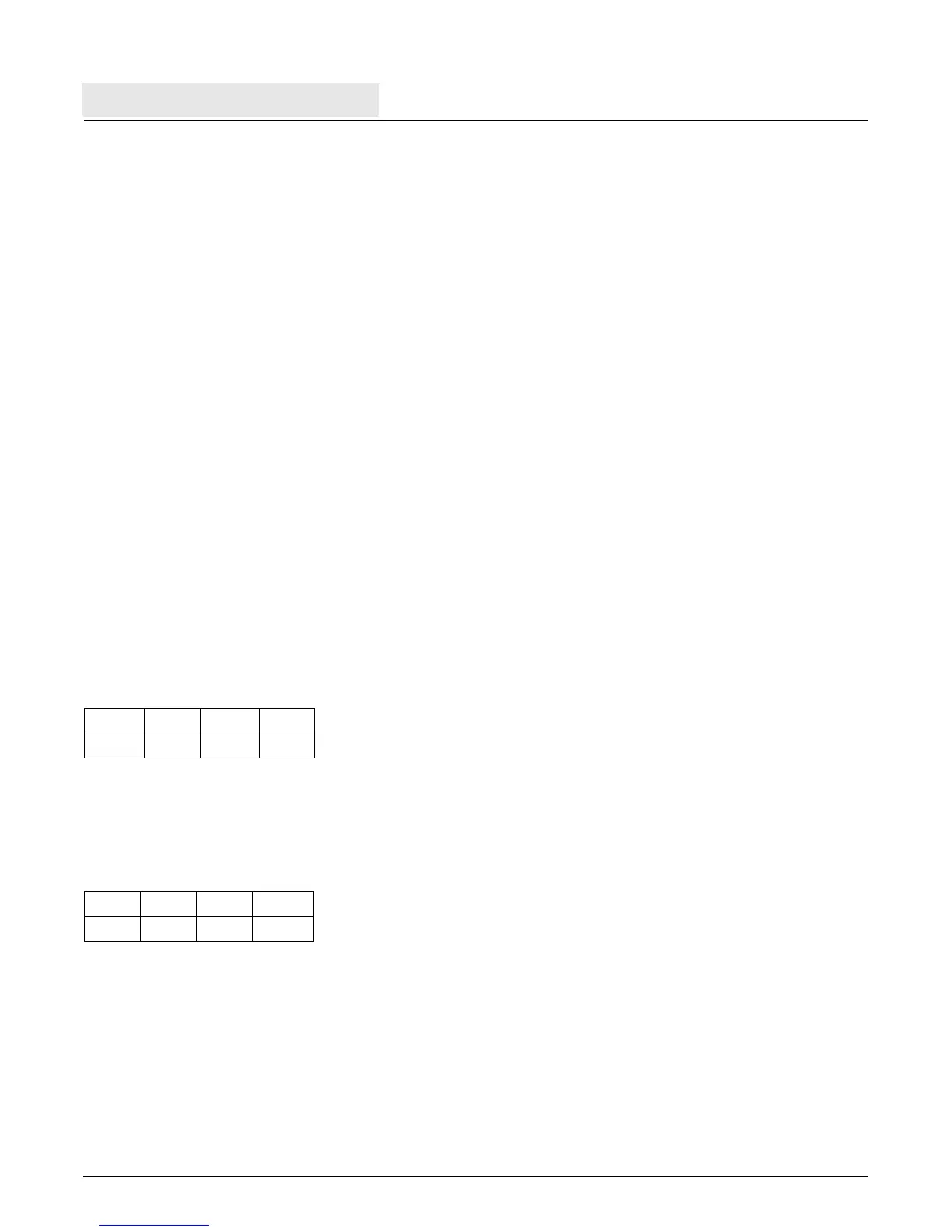

On the other hand, in the little endian mapping instruction p is arranged with the least significant byte (LSB) of the

instruction word at the lowest numbered address:

When an instruction is fetched from memory, the instruction must be placed in the instruction queue in the proper

order. The execution unit assumes that the MSB of an instruction word is at the lowest address. Therefore, when

instructions are fetched from little endian storage regions, the four bytes of an instruction word are reversed before

the instruction is decoded. In the PPC405, the byte reversal occurs between memory and the instruction cache unit

(ICU). The ICU always stores instructions in big endian format, regardless of whether the memory region

containing the instruction is programmed as big endian or little endian. Thus, the bytes are already in the proper

order when an instruction is transferred from the ICU to the decode stage of the pipeline.

Table 2-6. Big Endian Mapping

MSB LSB

0x00 0x01 0x02 0x03

Table 2-7. Little Endian Mapping

LSB MSB

0x00 0x01 0x02 0x03

Loading...

Loading...