AMCC Proprietary 401

Revision 1.02 - September 10, 2007

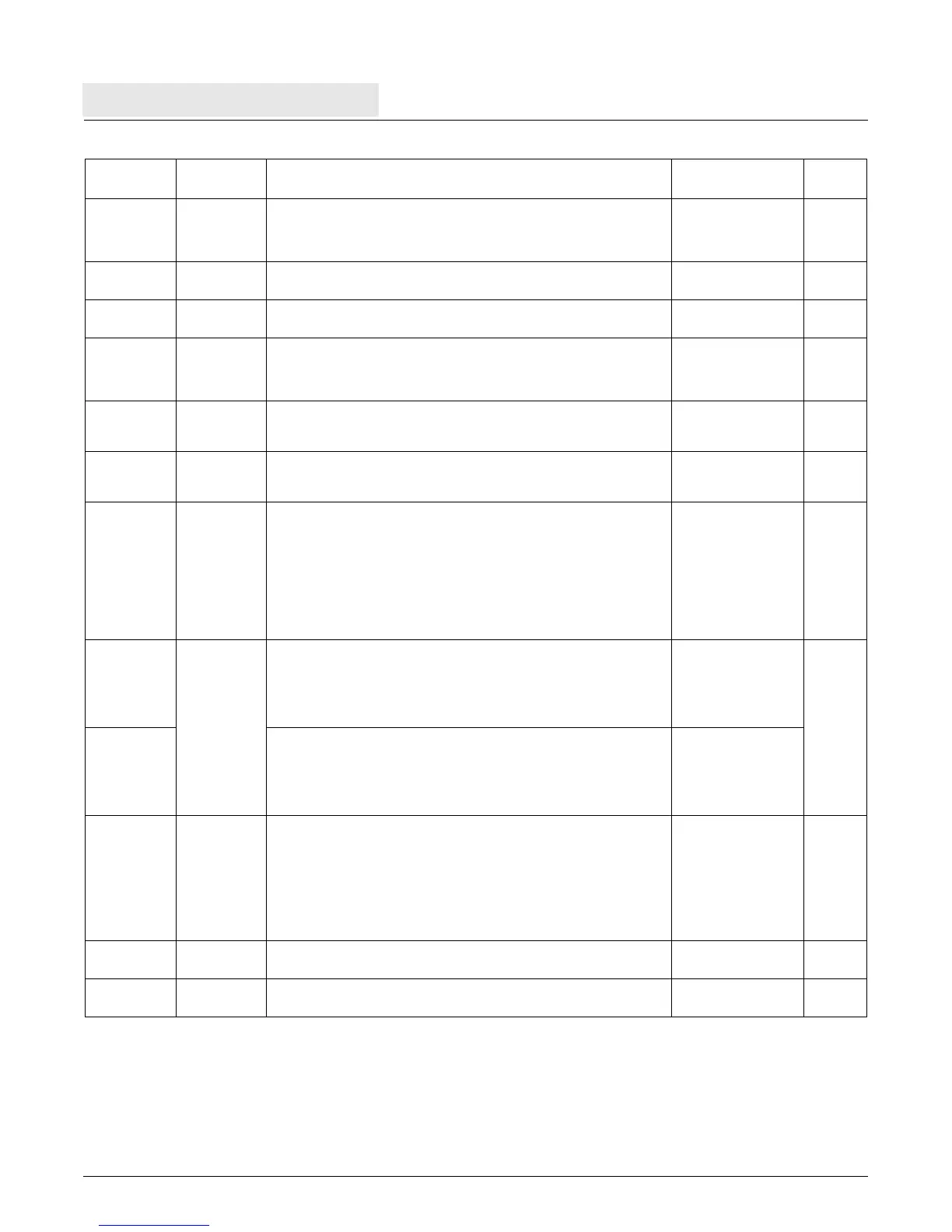

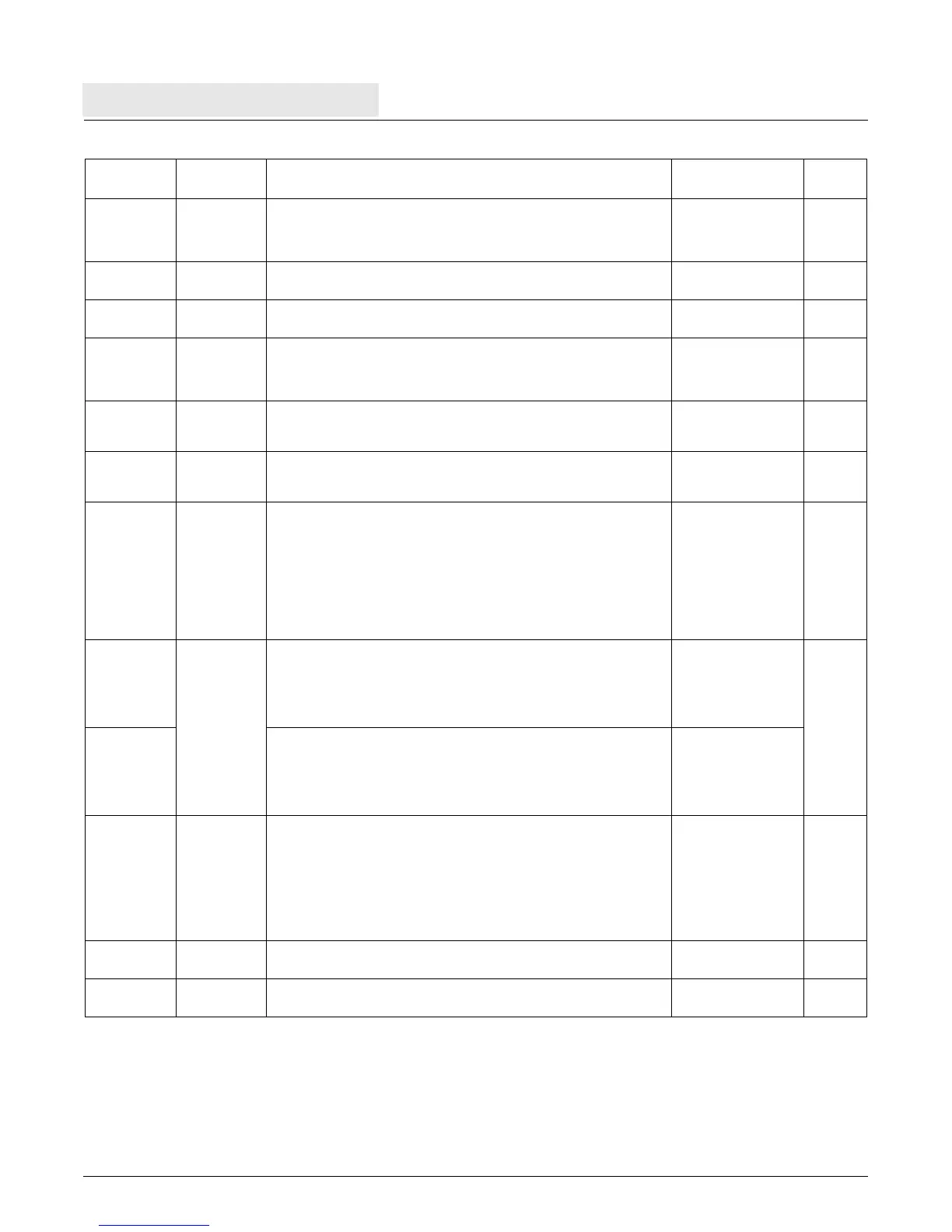

PPC405 Processor

Preliminary User’s Manual

mfspr RT, SPRN Move from SPR to RT,

(RT) ← (SPR(SPRN)).

Privileged for all SPRs except

LR, CTR, TBHU, TBLU, and XER.

272

mtdcr DCRN, RS Move to DCR from RS,

(DCR(DCRN))

← (RS).

270

mtmsr RS Move to MSR from RS,

(MSR)

← (RS).

271

mtspr SPRN, RS Move to SPR from RS,

(SPR(SPRN))

← (RS).

Privileged for all SPRs except

LR, CTR, and XER.

272

rfci Return from critical interrupt

(PC)

← (SRR2).

(MSR)

← (SRR3).

297

rfi Return from interrupt.

(PC)

← (SRR0).

(MSR) ← (SRR1).

298

tlbre RT, RA,WS If WS = 0:

Load TLBHI portion of the selected TLB entry into RT.

Load the PID register with the contents of the TID field of the selected

TLB entry.

(RT)

← TLBHI[(RA)]

(PID) ← TLB[(RA)]

TID

If WS = 1:

Load TLBLO portion of the selected TLB entry into RT.

(RT) ← TLBLO[(RA)]

335

tlbsx RT,RA,RB Search the TLB array for a valid entry which translates the EA

EA = (RA|0) + (RB).

If found,

(RT)

← Index of TLB entry.

If not found,

(RT) Undefined.

337

tlbsx. If found,

(RT) ← Index of TLB entry.

CR[CR0]

EQ

← 1.

If not found,

(RT) Undefined.

CR[CR0]

EQ

← 1.

CR[CR0]

LT,GT,SO

tlbwe RS, RA,WS If WS = 0:

Write TLBHI portion of the selected TLB entry from RS.

Write the TID field of the selected TLB entry from the PID register.

TLBHI[(RA)]

← (RS)

TLB[(RA)]

TID

← (PID)

24:31

If WS = 1:

Write TLBLO portion of the selected TLB entry from RS.

TLBLO[(RA)]

← (RS)

339

wrtee RS Write value of RS

16

to the External Enable

bit (MSR[EE]).

347

wrteei E Write value of E to the External Enable

bit (MSR[EE]).

348

Table B-4. Privileged Instructions (Continued)

Mnemonic Operands Function

Other Registers

Changed

Page

Loading...

Loading...