AMCC Proprietary 399

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

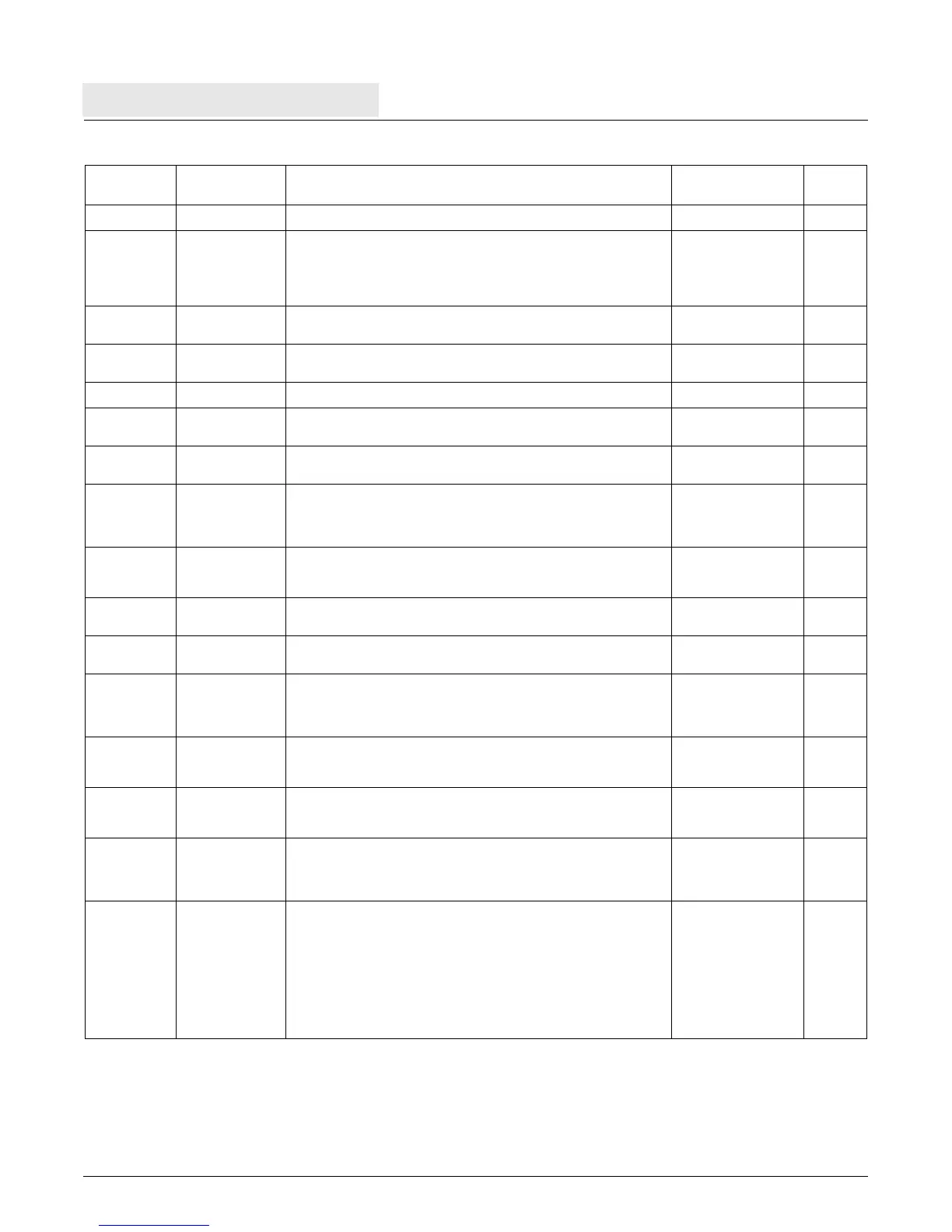

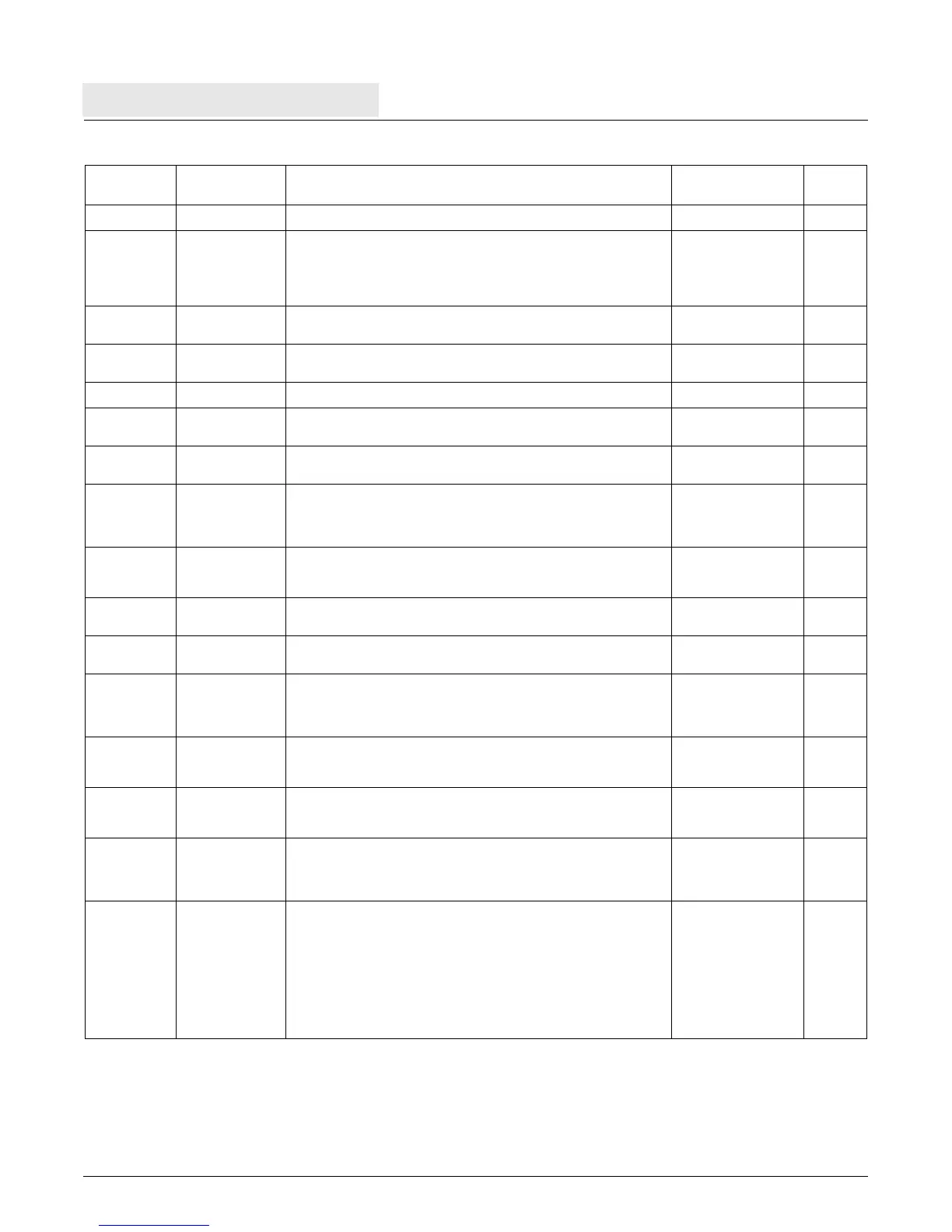

dcbz RA, RB Zero the data cache block which contains the EA (RA|0) + (RB). 208

eieio Storage synchronization. All loads and stores that precede the eieio

instruction complete before any loads and stores that follow the

instruction access main storage.

Implemented as sync, which is more restrictive.

215

icbi RA, RB Invalidate the instruction cache block which contains the EA

(RA|0) + (RB).

219

icbt RA, RB Load the instruction cache block which contains the EA

(RA|0) + (RB).

220

isync Synchronize execution context by flushing the prefetch queue. 224

mfdcr RT, DCRN Move from DCR to RT,

(RT) ← (DCR(DCRN)).

264

mfmsr RT Move from MSR to RT,

(RT) ← (MSR).

265

mfspr RT, SPRN Move from SPR to RT,

(RT)

← (SPR(SPRN)).

Privileged for all SPRs except

LR, CTR, TBHU, TBLU, and XER.

266

mftb RT Move the contents of a Time Base Register (TBR) into RT,

TBRN ← TBRF

5:9

|| TBRF

0:4

(RT) ← (TBR(TBRN))

268

mtdcr DCRN, RS Move to DCR from RS,

(DCR(DCRN))

← (RS).

270

mtmsr RS Move to MSR from RS,

(MSR) ← (RS).

271

mtspr SPRN, RS Move to SPR from RS,

(SPR(SPRN)) ← (RS).

Privileged for all SPRs except

LR, CTR, and XER.

272

rfci Return from critical interrupt

(PC)

← (SRR2).

(MSR)

← (SRR3).

297

rfi Return from interrupt.

(PC) ← (SRR0).

(MSR)

← (SRR1).

298

tlbia All of the entries in the TLB are invalidated and become unavailable

for translation by clearing the valid (V) bit in the TLBHI portion of

each TLB entry. The rest of the fields in the TLB entries are

unmodified.

334

tlbre RT, RA,WS If WS = 0:

Load TLBHI portion of the selected TLB entry into RT.

Load the PID register with the contents of the TID field of the

selected TLB entry.

(RT)

← TLBHI[(RA)]

(PID) ← TLB[(RA)]

TID

If WS = 1:

Load TLBLO portion of the selected TLB entry into RT.

(RT)

← TLBLO[(RA)]

335

Table B-3. Instructions in the IBM PowerPC Embedded Environment (Continued)

Mnemonic Operands Function

Other Registers

Changed

Page

Loading...

Loading...