146 AMCC Proprietary

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

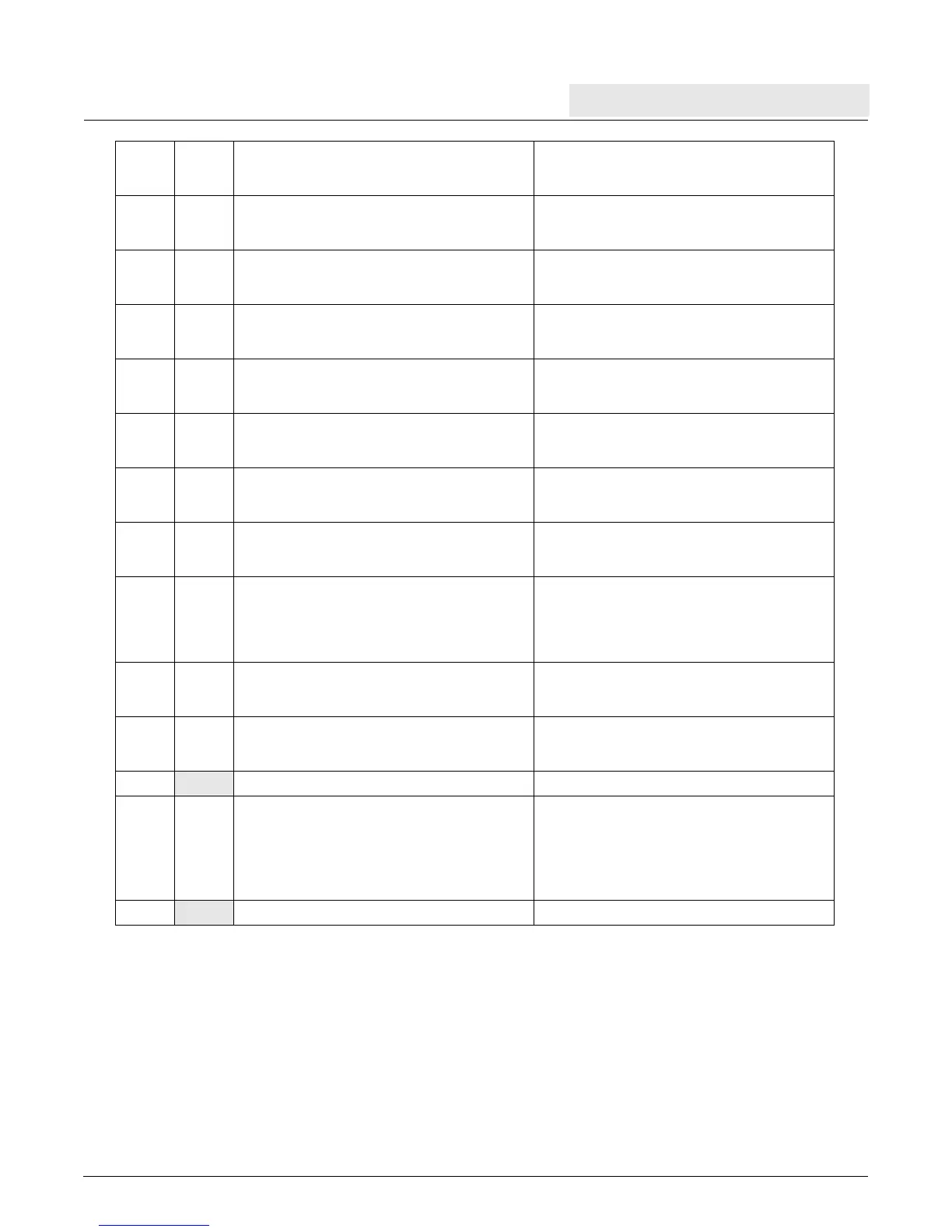

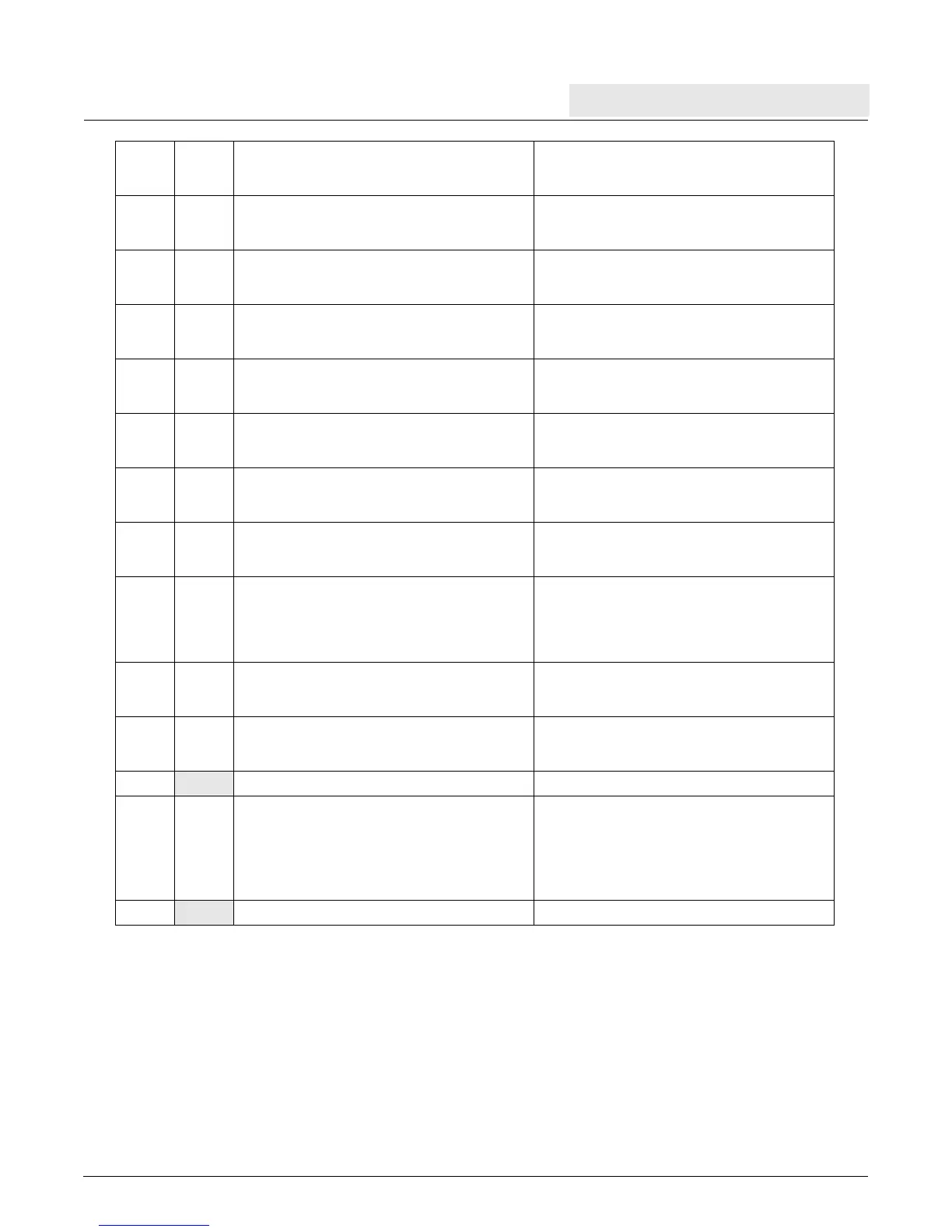

3TIE

Trap Instruction Debug Event:

0 Event did not occur

1 Event occurred

4 UDE

Unconditional Debug Event:

0 Event did not occur

1 Event occurred

5IA1

IAC1 Debug Event:

0 Event did not occur

1 Event occurred

6IA2

IAC2 Debug Event:

0 Event did not occur

1 Event occurred

7 DR1

DAC1 Read Debug Event:

0 Event did not occur

1 Event occurred

8DW1

DAC1 Write Debug Event:

0 Event did not occur

1 Event occurred

9 DR2

DAC2 Read Debug Event:

0 Event did not occur

1 Event occurred

10 DW2

DAC2 Write Debug Event:

0 Event did not occur

1 Event occurred

11 IDE

Imprecise Debug Event:

0 No circumstance that would cause a debug

event (if MSR[DE] = 1) occurred

1 A debug event would have occurred, but debug

exceptions were disabled (MSR[DE] = 0)

12 IA3

IAC3 Debug Event:

0 Event did not occur

1 Event occurred

13 IA4

IAC4 Debug Event:

0 Event did not occur

1 Event occurred

14:21

Reserved

22:23 MRR

Most Recent Reset:

No reset has occurred since last cleared by soft-

ware.

0 Core reset

1 Chip reset

System reset

This field is set to a value, indicating the type of

reset, when a reset occurs.

24:31

Reserved

Loading...

Loading...