AMCC Proprietary 222

Revision 1.02 - September 10, 2007

PPC405 Processor

icread

Instruction Cache Read

Preliminary User’s Manual

icread

Instruction Cache Read

EA ← (RA|0) + (RB)

if ((CCR0[CIS] = 0)

∧ (CCR0[CWS] = 0)) then (ICDBDR) ← (i-cache data, way A)

if ((CCR0[CIS] = 0)

∧ (CCR0[CWS] = 1)) then (ICDBDR) ← (i-cache data, way B)

if ((CCR0[CIS] = 1) ∧ (CCR0[CWS] = 0)) then (ICDBDR) ← (i-cache tag, way A)

if ((CCR0[CIS] = 1)

∧ (CCR0[CWS] = 1)) then (ICDBDR) ← (i-cache tag, way B)

An effective address (EA) is formed by adding an index to a base address. The index is the contents of register RB.

The base address is 0 if the RA field is 0 and is the contents of register RA otherwise.

This instruction is a debugging tool for reading the instruction cache entries for the congruence class specified by

EA

18:26

. The cache information is read into the Instruction Cache Debug Data Register (ICDBDR), from where it

can be read into a GPR using the extended mnemonic mficdbdr.

If CCR0[CIS] = 0, the information is a word of instruction cache data from the addressed line. The word is specified

by EA

27:29

. If CCR0[CWS] = 0, the data is from the A-way, otherwise from the B-way.

If (CCR0[CIS] = 1), the information is a cache tag from the addressed congruence class. If (CCR0[CWS] = 0), the

tag is from the A-way, otherwise from the B-way.

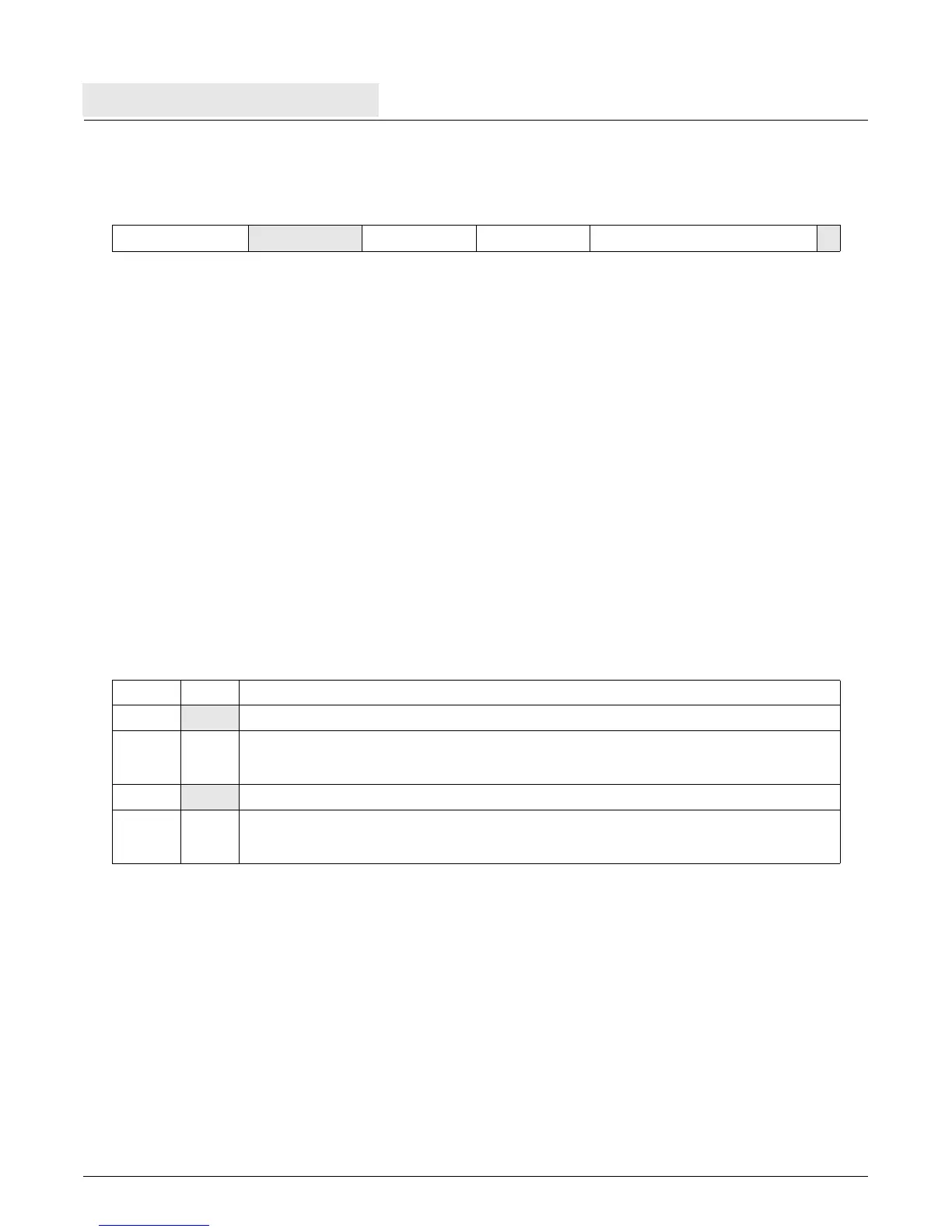

Instruction cache tag information is placed in the ICDBDR as shown:

If instruction bit 31 contains 1, the contents of CR[CR0] are undefined.

Registers Altered

•ICDBDR

Invalid Instruction Forms

• Reserved fields

Programming Note

Execution of this instruction is privileged.

The instruction pipeline does not automatically wait for data from icread to arrive at the ICDBDR before attempting

to use the contents of the ICDBDR. Therefore, insert an isync instruction between icread and mficdbdr.

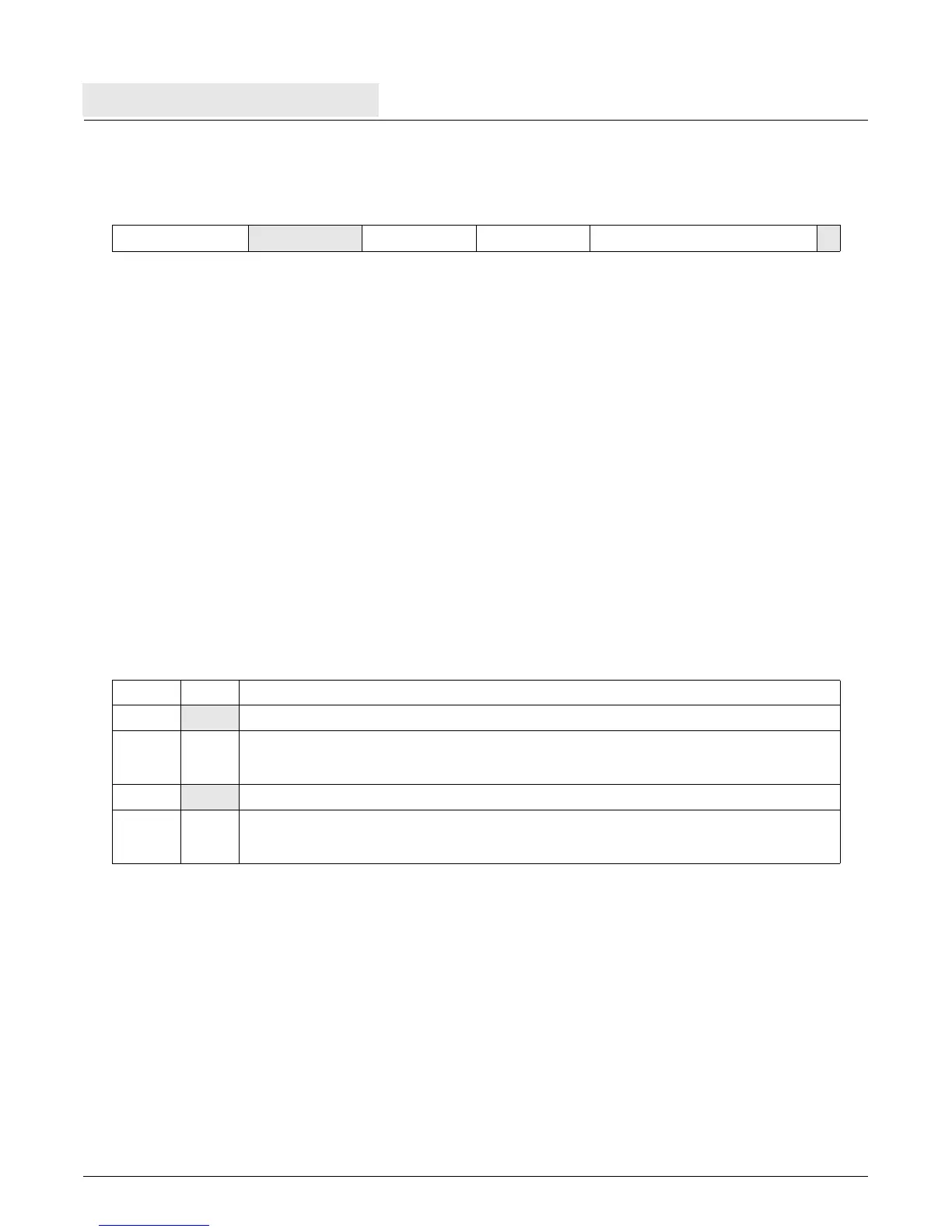

icread RA, RB

31

RA RB 998

0 6 11 16 21 31

0:21 TAG Cache Tag

22:26

Reserved

27 V

Cache Line Valid

0Not valid

1Valid

28:30

Reserved

31 LRU

Least Recently Used (LRU)

0 A-way LRU

1 B-way LRU

Loading...

Loading...