AMCC Proprietary 288

Revision 1.02 - September 10, 2007

PPC405 Processor

nmachhw

Negative Multiply Accumulate High Halfword to Word Modulo

Preliminary User’s Manual

nmachhw

Negative Multiply Accumulate High Halfword to Word Modulo Signed

nprod

0:31

← –((RA)

0:15

x (RB)

0:15

) signed

temp

0:32

← nprod

0:31

+ (RT)

(RT)

← temp

1:32

The high-order halfword of RA is multiplied by the high-order halfword of RB. The negated signed product is

summed with the contents of RT and the sum is stored in a 33-bit temporary register. The contents of RT are

replaced by the low-order 32 bits of the temporary register.

Registers Altered

•RT

• CR[CR0]

LT, GT, EQ, SO

if Rc contains 1

• XER[SO, OV] if OE contains 1

Architecture Note

This instruction is part of the Multiply-Accumulate instruction set extensions and complies with the architectural

requirements for APUs of the PowerPC Embedded Environment. As such, it is not part of the PowerPC Architec-

ture, nor is it part of the PowerPC Embedded Environment. Programs that use this instruction may not be portable

to other implementations.

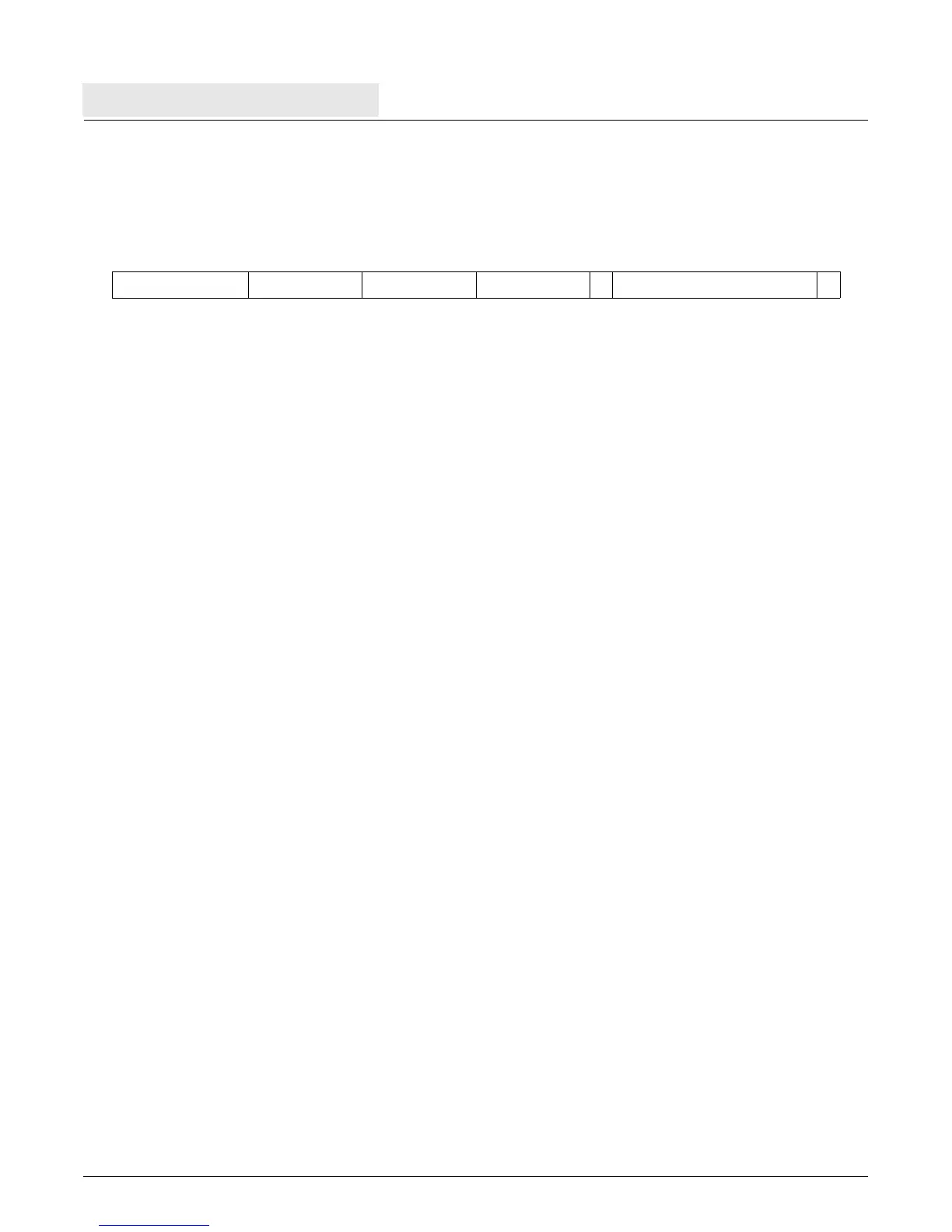

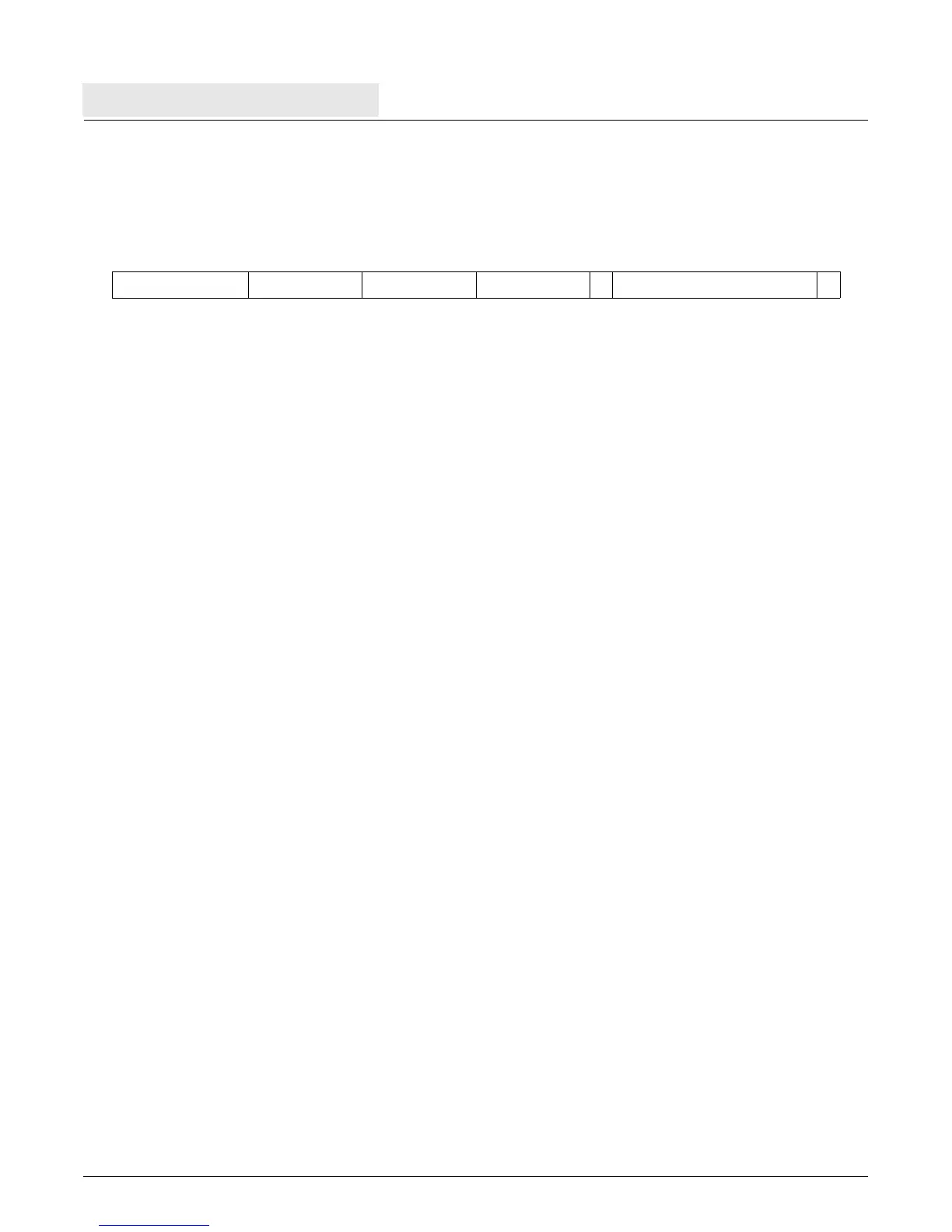

nmachhw RT, RA, RB OE=0, Rc=0

nmachhw. RT, RA, RB OE=0, Rc=1

nmachhwo RT, RA, RB OE=1, Rc=0

nmachhwo. RT, RA, RB OE=1, Rc=1

4RTRARBOE46Rc

0 6 11 16 21 22 31

Loading...

Loading...