UM0306 Universal synchronous asynchronous receiver transmitter (USART)

413/519

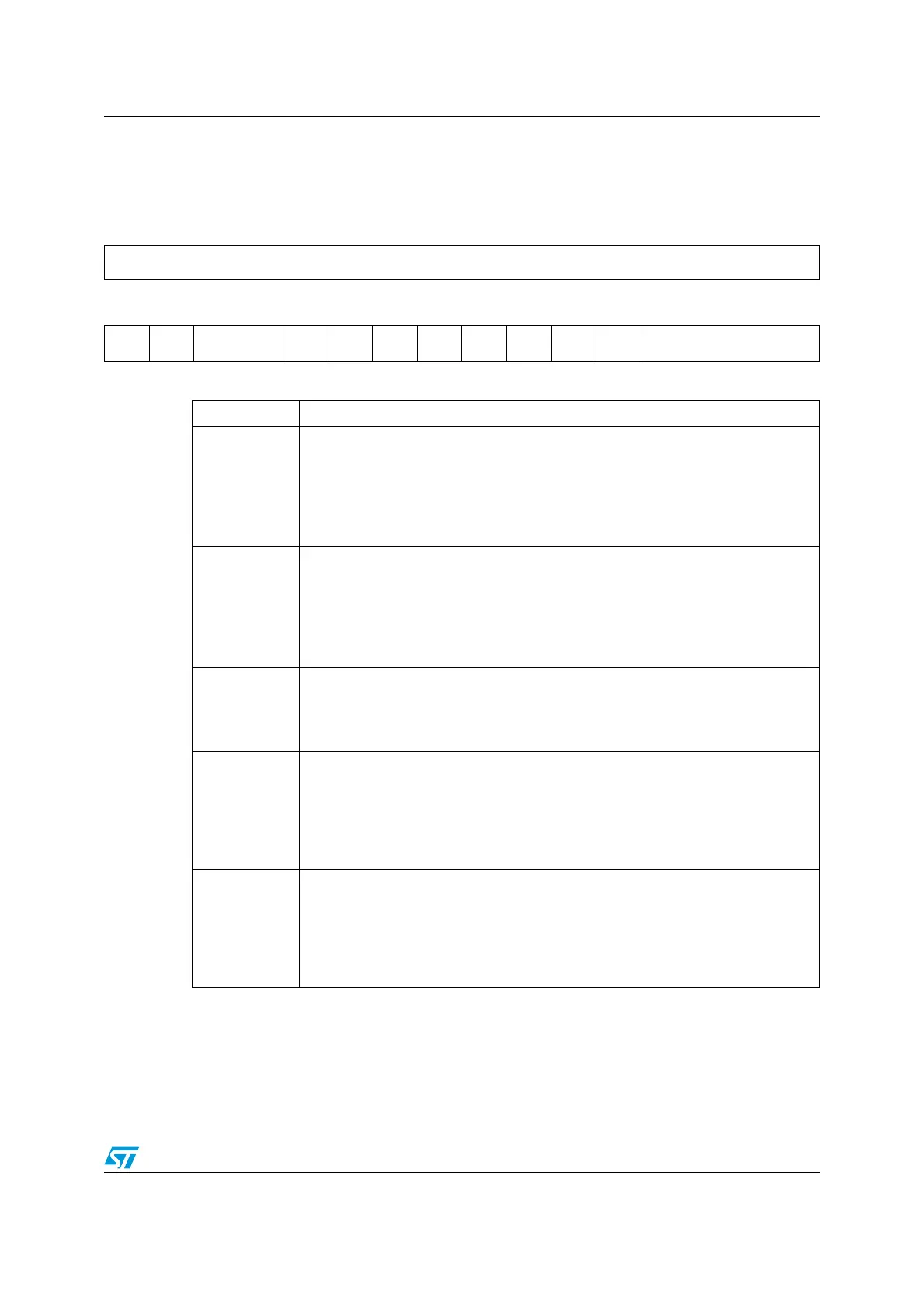

17.4.5 Control register 2 (USART_CR2)

Address Offset: 10h

Reset Value: 0000h

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

1514131211109876543210

Res. LINEN STOP[1:0]

CLK

EN

CPOL CPHA LBCL Res. LBDIE LBDL Res. ADD[3:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:15 Reserved, forced by hardware to 0.

Bit 14

LINEN: LIN mode enable

This bit is set and cleared by software.

0: LIN mode disabled

1: LIN mode enabled

The LIN mode enables the capability to send LIN Synch Breaks (13 low bits)

using the SBK bit in the USART_CR1 register, and to detect LIN Sync breaks.

Bits 13:12

STOP: STOP bits.

These bits are used for programming the stop bits.

00: 1 Stop bit

01: 0.5 Stop bit

10: 2 Stop bits

11: 1.5 Stop bit

Bit 11

CLKEN: Clock Enable.

This bit allows the user to enable the SCLK pin.

0: SCLK pin disabled

1: SCLK pin enabled

Bit 10

CPOL: Clock Polarity.

This bit allows the user to select the polarity of the clock output on the SCLK pin

in synchronous mode. It works in conjunction with the CPHA bit to produce the

desired clock/data relationship

0: Steady low value on SCLK pin outside transmission window.

1: Steady high value on SCLK pin outside transmission window.

Bit 9

CPHA: Clock Phase

This bit allows the user to select the phase of the clock output on the SCLK pin in

synchronous mode. It works in conjunction with the CPOL bit to produce the

desired clock/data relationship (see figures 152 to 155)

0: The first clock transition is the first data capture edge.

1: The second clock transition is the first data capture edge.

Loading...

Loading...