AMCC Proprietary 233

Revision 1.02 - September 10, 2007

PPC405 Processor

lhbrx

Load Halfword Byte-Reverse Indexed

Preliminary User’s Manual

lhbrx

Load Halfword Byte-Reverse Indexed

EA ← (RA|0) + (RB)

(RT)

←

16

0 || MS(EA +1,1) || MS(EA,1)

An effective address (EA) is formed by adding an index to a base address. The index is the contents of register RB.

The base address is 0 if the RA field is 0 and is the contents of register RA otherwise.

The halfword at the EA is byte-reversed. The resulting halfword is extended to 32 bits by concatenating 16 0-bits to

its left. The result is placed into register RT.

If instruction bit 31 contains 1, the contents of CR[CR0] are undefined.

Registers Altered

•RT

Invalid Instruction Forms

• Reserved fields

Architecture Note

This instruction is part of the PowerPC User Instruction Set Architecture.

l

hbrx RT, RA, RB

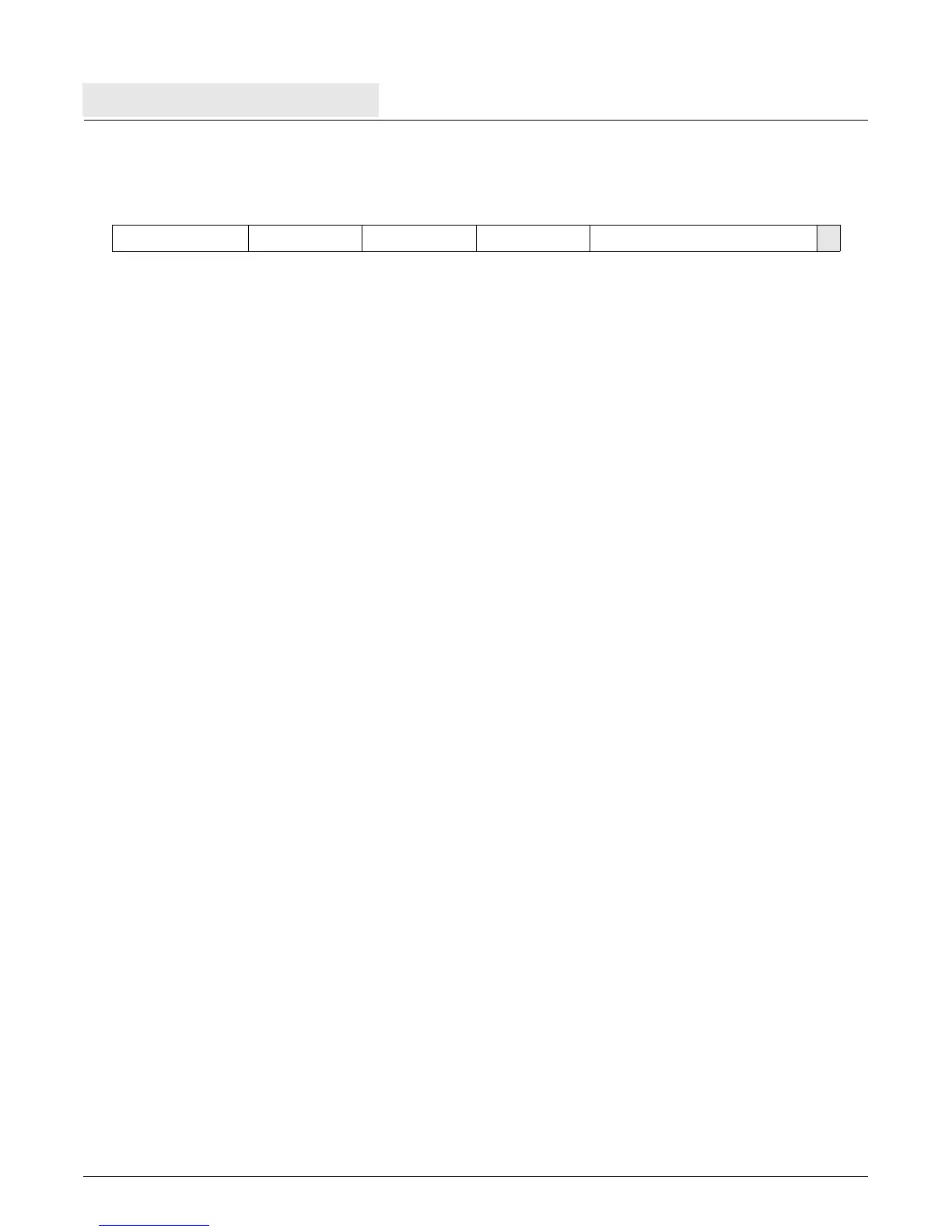

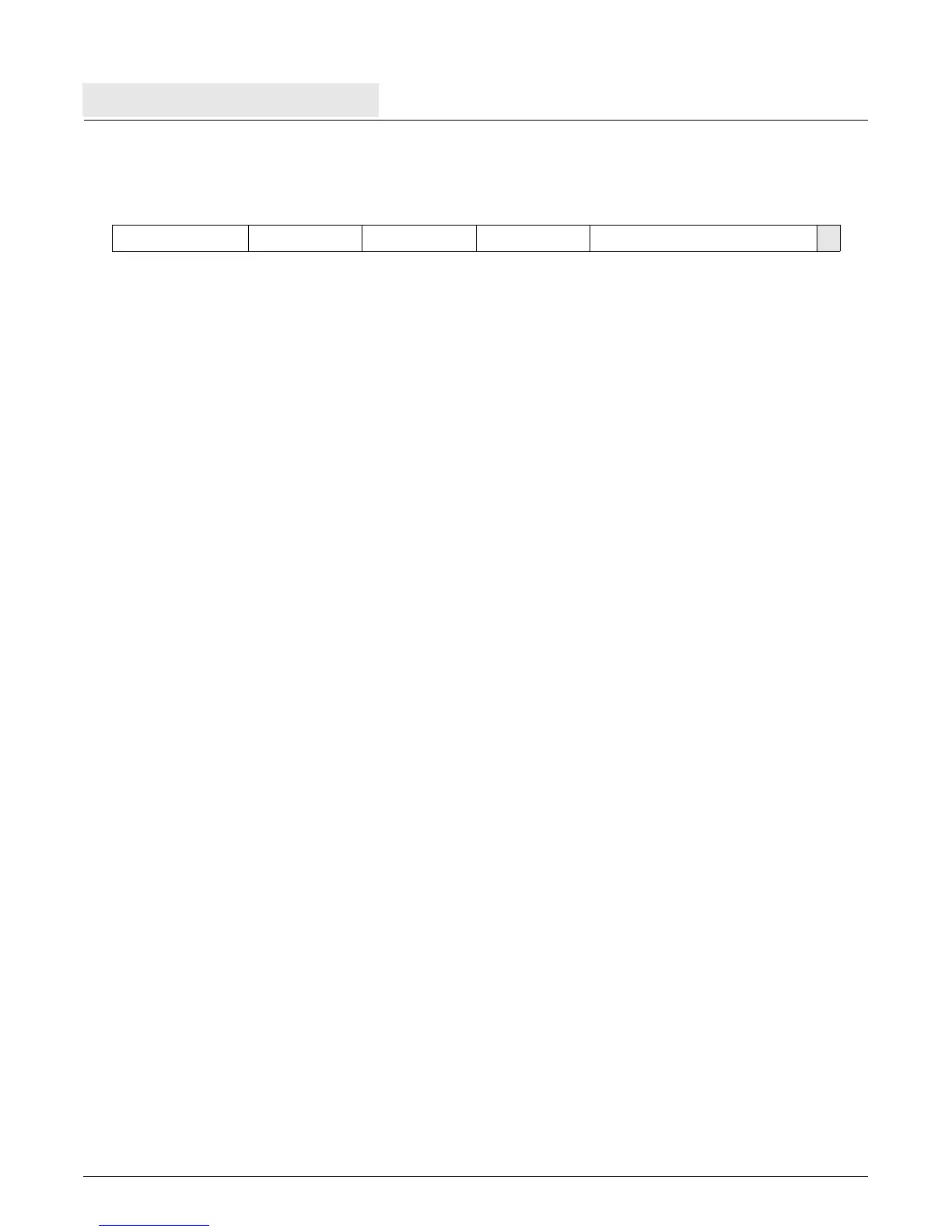

31 RT RA RB 790

0 6 11 16 21 31

Loading...

Loading...