AMCC Proprietary 373

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

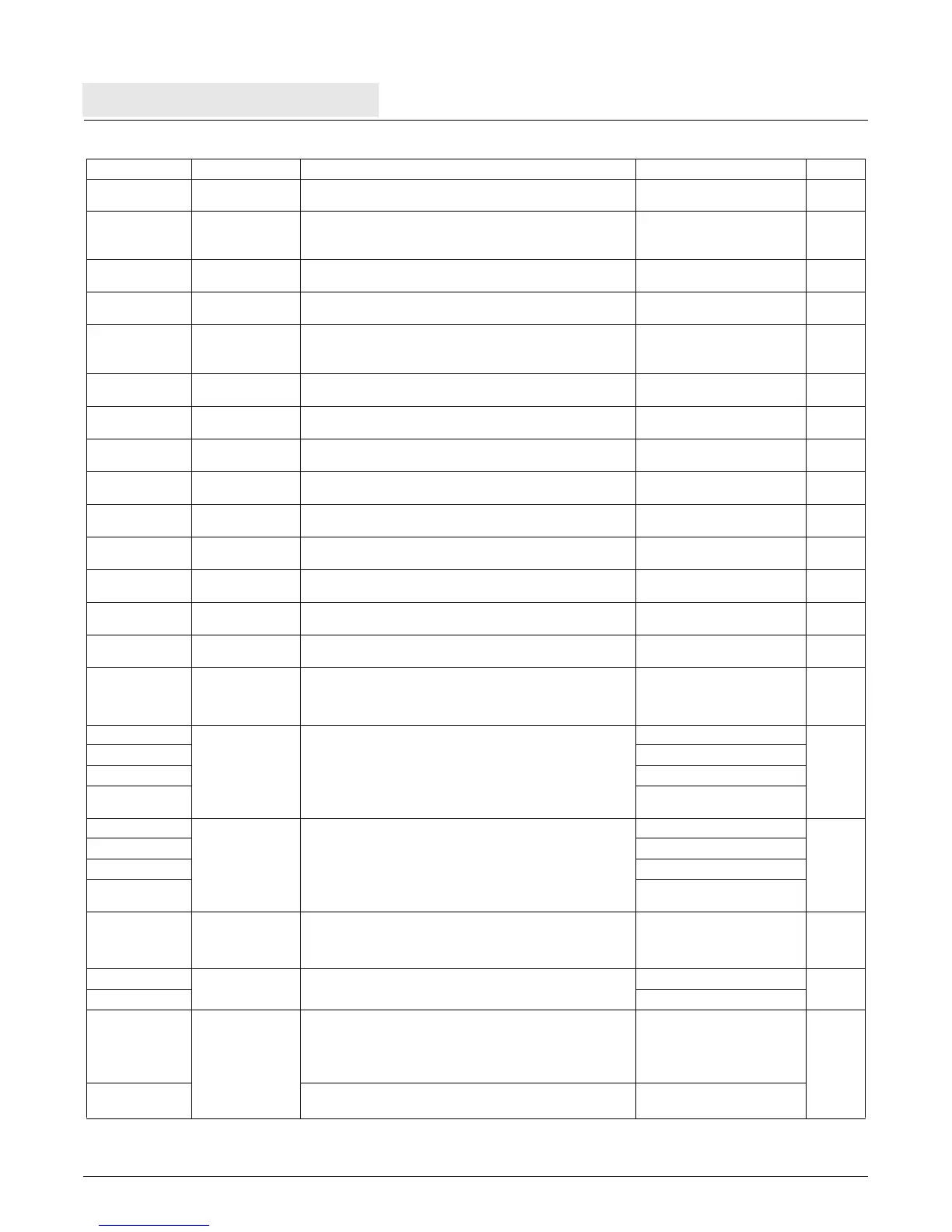

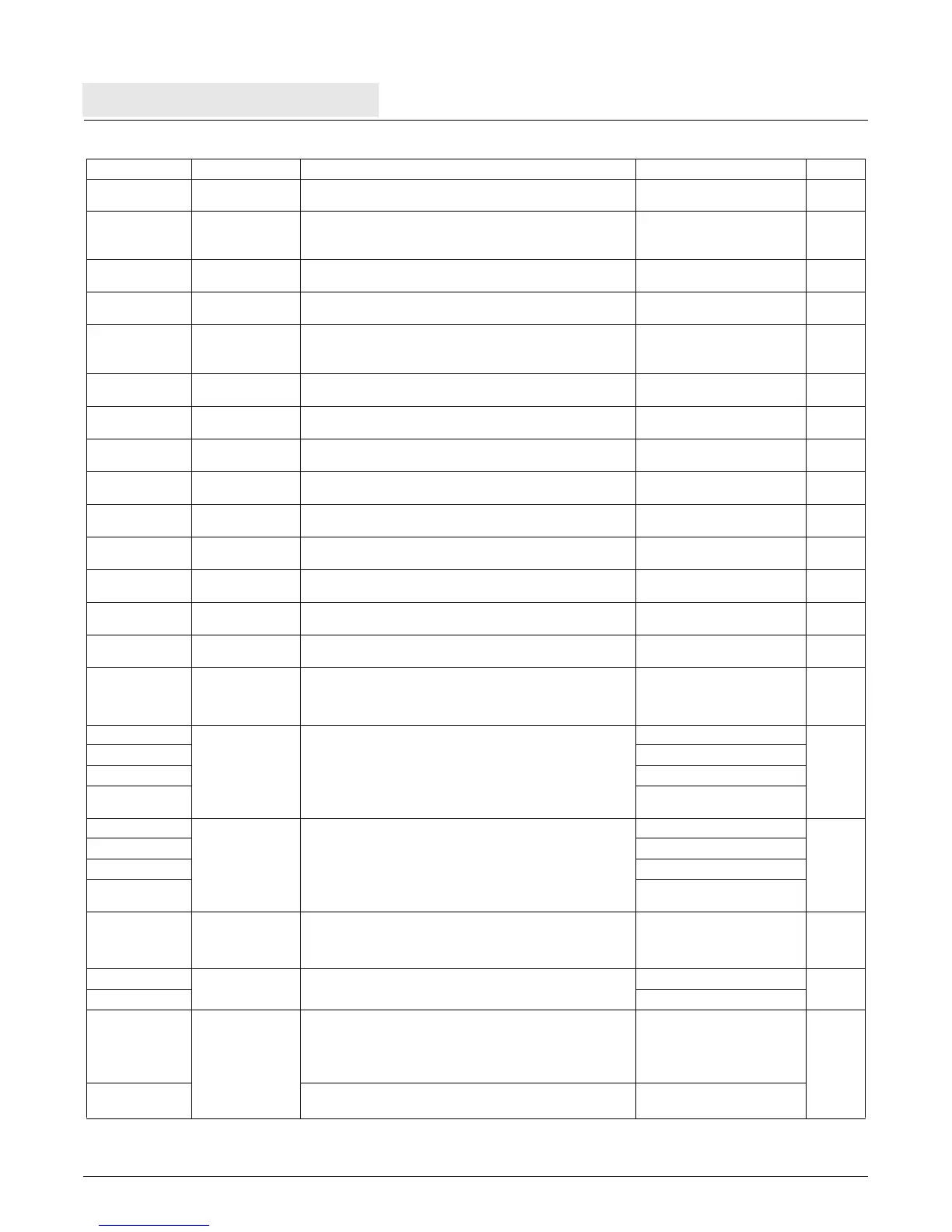

crnor BT, BA, BB NOR bit (CR

BA

) with (CR

BB

).

Place result in CR

BT

.

197

crnot bx, by Condition register not.

Extended mnemonic for

crnor bx,by,by

197

cror BT, BA, BB OR bit (CR

BA

) with (CR

BB

).

Place result in CR

BT

.

198

crorc BT, BA, BB OR bit (CR

BA

) with ¬(CR

BB

).

Place result in CR

BT

.

199

crset bx Condition register set.

Extended mnemonic for

creqv bx,bx,bx

195

crxor BT, BA, BB XOR bit (CR

BA

) with (CR

BB

).

Place result in CR

BT

.

200

dcba RA, RB Speculatively establish the data cache block which contains

the effective address (RA|0) + (RB).

201

dcbf RA, RB Flush (store, then invalidate) the data cache block which

contains the effective address (RA|0) + (RB).

203

dcbi RA, RB Invalidate the data cache block which contains the effective

address (RA|0) + (RB).

204

dcbst RA, RB Store the data cache block which contains the effective

address (RA|0) + (RB).

205

dcbt RA, RB Load the data cache block which contains the effective

address (RA|0) + (RB).

206

dcbtst RA,RB Load the data cache block which contains the effective

address (RA|0) + (RB).

207

dcbz RA, RB Zero the data cache block which contains the effective

address (RA|0) + (RB).

208

dccci RA, RB Invalidate the data cache congruence class associated with

the effective address (RA|0) + (RB).

210

dcread RT, RA, RB Read either tag or data information from the data cache

congruence class associated with the effective address

(RA|0) + (RB).

Place the results in RT.

211

divw RT, RA, RB Divide (RA) by (RB), signed.

Place result in RT.

213

divw. CR[CR0]

divwo XER[SO, OV]

divwo. CR[CR0]

XER[SO, OV]

divwu RT, RA, RB Divide (RA) by (RB), unsigned.

Place result in RT.

214

divwu. CR[CR0]

divwuo XER[SO, OV]

divwuo. CR[CR0]

XER[SO, OV]

eieio Storage synchronization. All loads and stores that precede

the eieio instruction complete before any loads and stores

that follow the instruction access main storage.

Implemented as sync, which is more restrictive.

215

eqv RA, RS, RB Equivalence of (RS) with (RB).

(RA)

←¬((RS) ⊕ (RB))

216

eqv. CR[CR0]

extlwi RA, RS, n, b Extract and left justify immediate. (n > 0)

(RA)

0:n−1

← (RS)

b:b+n−1

(RA)

n:31

←

32−n

0

Extended mnemonic for

rlwinm RA,RS,b,0,n−1

300

extlwi. Extended mnemonic for

rlwinm. RA,RS,b,0,n−1

CR[CR0]

Table A-1. PPC405 Instruction Syntax Summary (Continued)

Mnemonic Operands Function Other Registers Changed Page

Loading...

Loading...