374 AMCC Proprietary

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

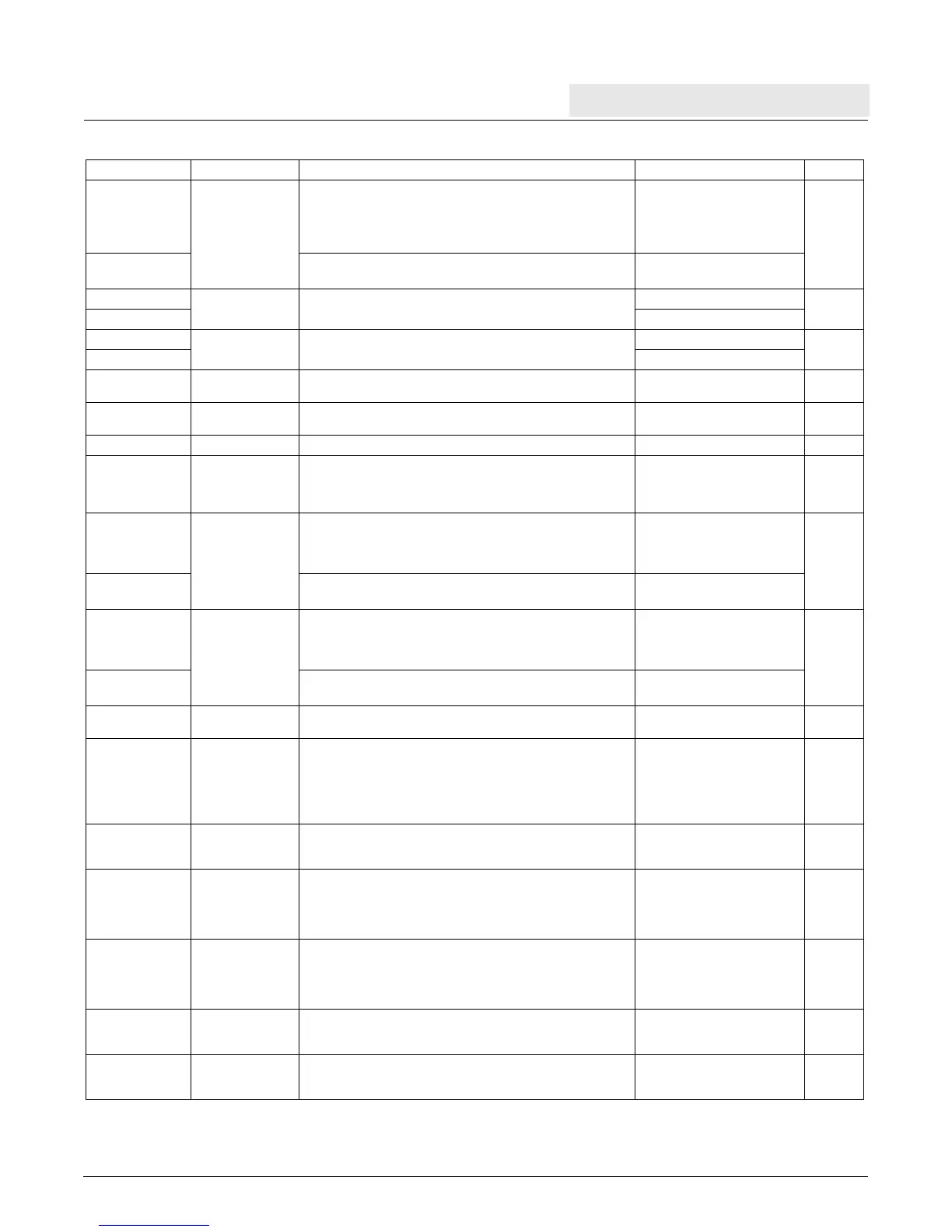

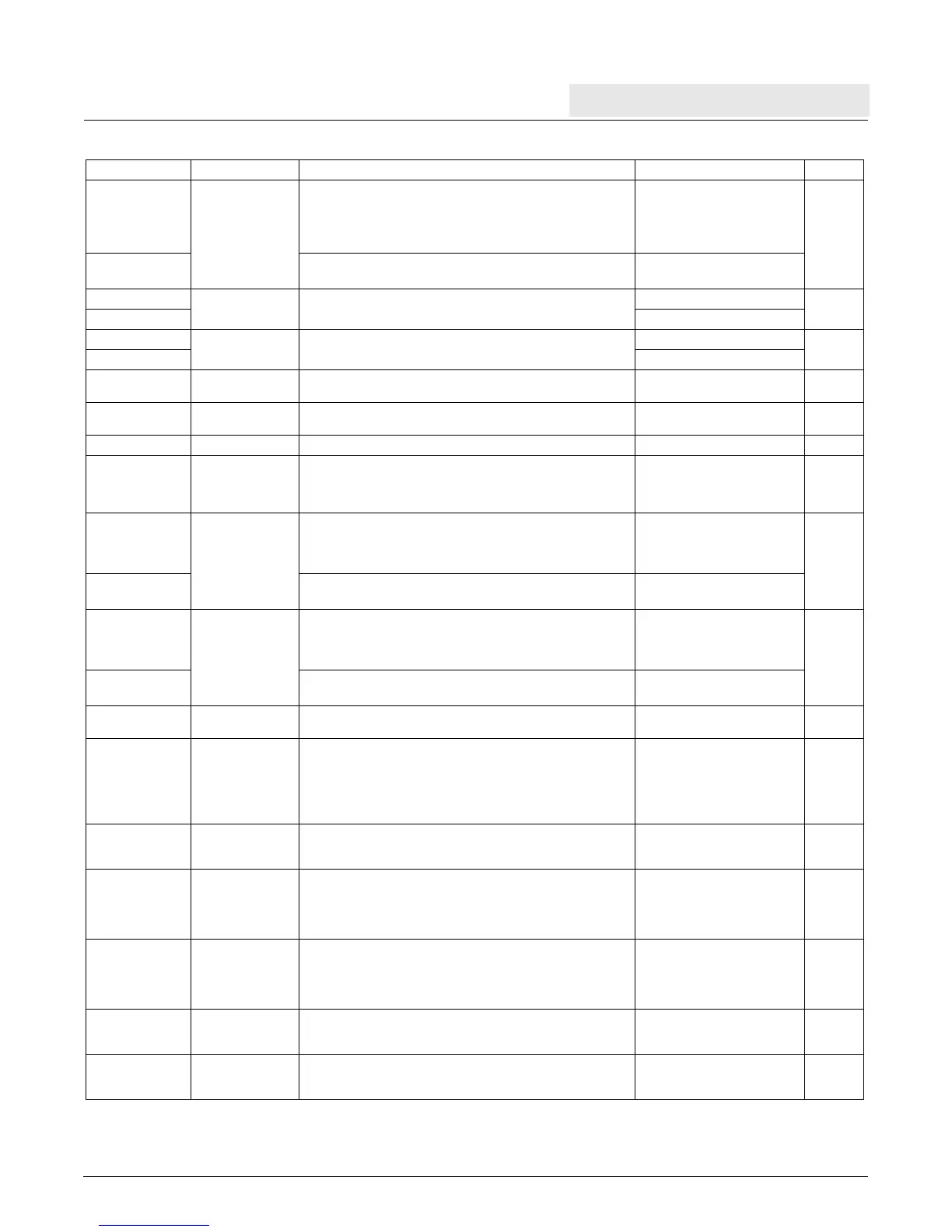

extrwi RA, RS, n, b Extract and right justify immediate. (n > 0)

(RA)

32−n:31

← (RS)

b:b+n−1

(RA)

0:31−n

←

32−n

0

Extended mnemonic for

rlwinm RA,RS,b+n,32−n,31

300

extrwi. Extended mnemonic for

rlwinm. RA,RS,b+n,32−n,31

CR[CR0]

extsb RA, RS Extend the sign of byte (RS)

24:31

.

Place the result in RA.

217

extsb. CR[CR0]

extsh RA, RS Extend the sign of halfword (RS)

16:31

.

Place the result in RA.

218

extsh. CR[CR0]

icbi RA, RB Invalidate the instruction cache block which contains the

effective address (RA|0) + (RB).

219

icbt RA, RB Load the instruction cache block which contains the

effective address (RA|0) + (RB).

220

iccci RA, RB Invalidate instruction cache. 221

icread RA, RB Read either tag or data information from the instruction

cache congruence class associated with the effective

address (RA|0) + (RB).

Place the results in ICDBDR.

222

inslwi RA, RS, n, b Insert from left immediate. (n > 0)

(RA)

b:b+n−1

← (RS)

0:n−1

Extended mnemonic for

rlwimi RA,RS,32−b,b,b+n−1

299

inslwi. Extended mnemonic for

rlwimi. RA,RS,32−b,b,b+n−1

CR[CR0]

insrwi RA, RS, n, b Insert from right immediate. (n > 0)

(RA)

b:b+n−1

← (RS)

32−n:31

Extended mnemonic for

rlwimi RA,RS,32−b−n,b,b+n−1

299

insrwi. Extended mnemonic for

rlwimi. RA,RS,32−b−n,b,b+n−1

CR[CR0]

isync Synchronize execution context by flushing the prefetch

queue.

224

la RT, D(RA) Load address. (RA ≠ 0)

D is an offset from a base address that is assumed to be

(RA).

(RT)

← (RA) + EXTS(D)

Extended mnemonic for

addi RT,RA,D

164

lbz RT, D(RA) Load byte from EA = (RA|0) + EXTS(D) and pad left with

zeroes,

(RT)

←

24

0|| MS(EA,1).

225

lbzu RT, D(RA) Load byte from EA = (RA|0) + EXTS(D) and pad left with

zeroes,

(RT)

←

24

0|| MS(EA,1).

Update the base address,

(RA)

← EA.

226

lbzux RT, RA, RB Load byte from EA = (RA|0) + (RB) and pad left with

zeroes,

(RT)

←

24

0|| MS(EA,1).

Update the base address,

(RA)

← EA.

227

lbzx RT, RA, RB Load byte from EA = (RA|0) + (RB) and pad left with

zeroes,

(RT) ←

24

0|| MS(EA,1).

228

lha RT, D(RA) Load halfword from EA = (RA|0) + EXTS(D) and sign

extend,

(RT)

← EXTS(MS(EA,2)).

229

Table A-1. PPC405 Instruction Syntax Summary (Continued)

Mnemonic Operands Function Other Registers Changed Page

Loading...

Loading...