AMCC Proprietary 375

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

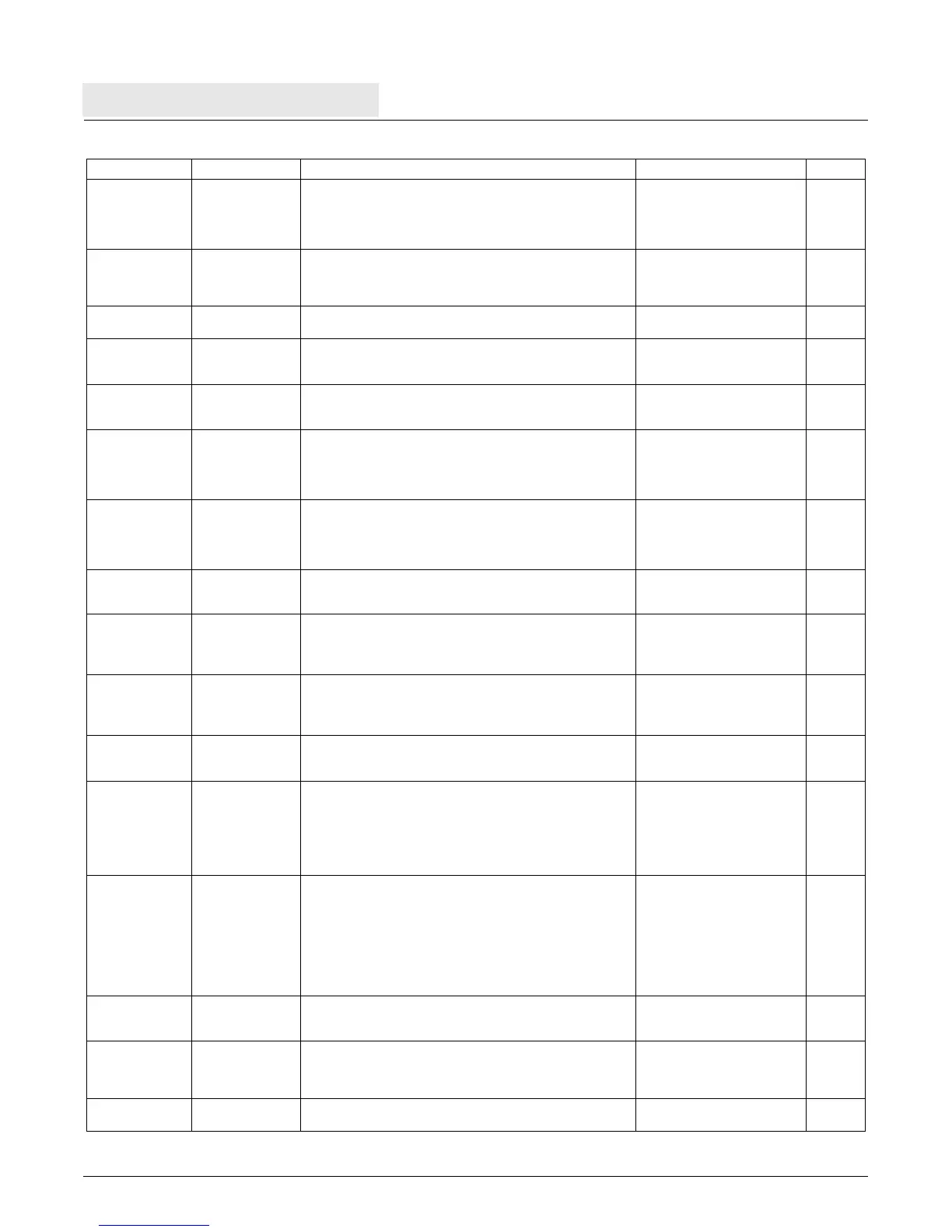

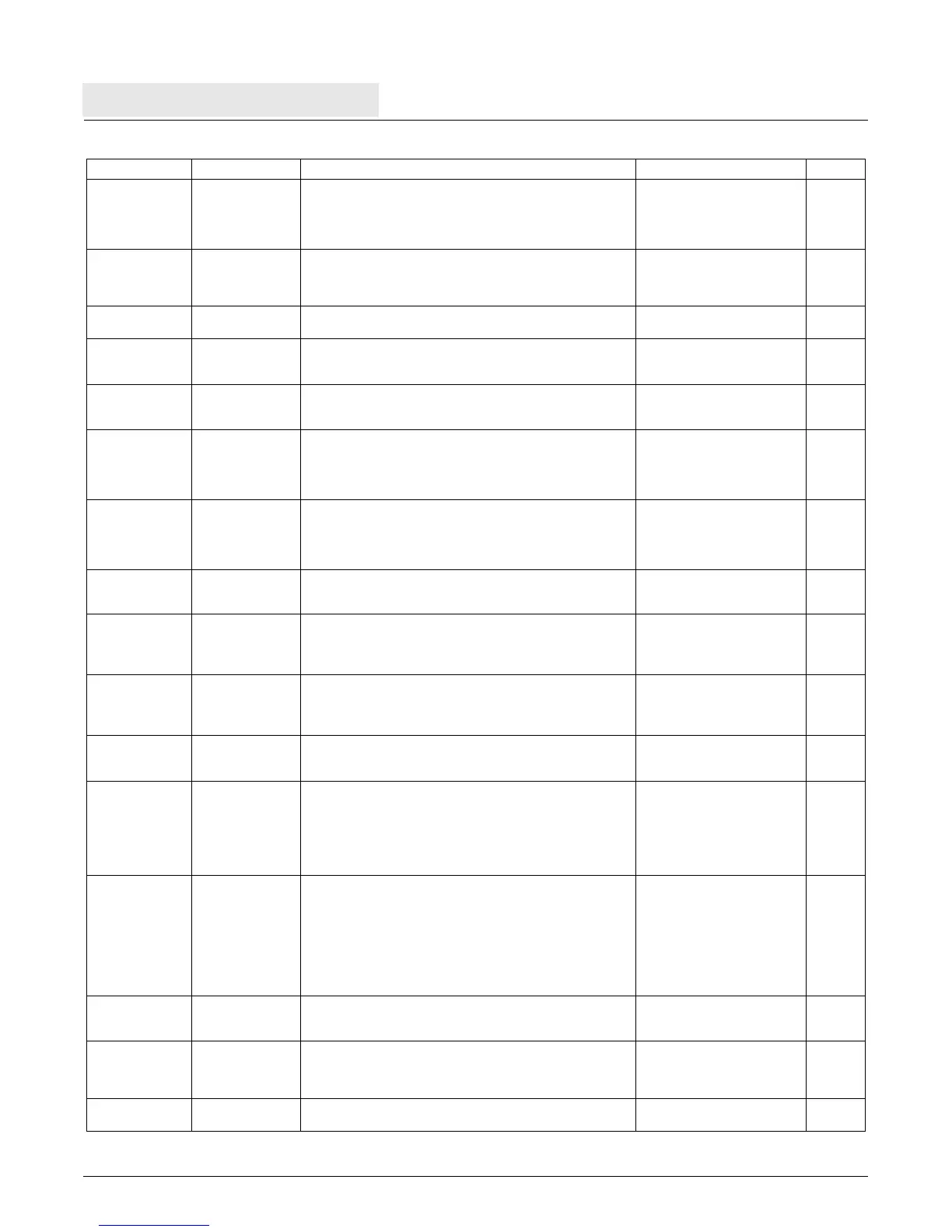

lhau RT, D(RA) Load halfword from EA = (RA|0) + EXTS(D) and sign

extend,

(RT)

← EXTS(MS(EA,2)).

Update the base address,

(RA)

← EA.

230

lhaux RT, RA, RB Load halfword from EA = (RA|0) + (RB) and sign extend,

(RT)

← EXTS(MS(EA,2)).

Update the base address,

(RA) ← EA.

231

lhax RT, RA, RB Load halfword from EA = (RA|0) + (RB) and sign extend,

(RT)

← EXTS(MS(EA,2)).

232

lhbrx RT, RA, RB Load halfword from EA = (RA|0) + (RB), then reverse byte

order and pad left with zeroes,

(RT)

←

16

0 || MS(EA+1,1) || MS(EA,1).

233

lhz RT, D(RA) Load halfword from EA = (RA|0) + EXTS(D) and pad left

with zeroes,

(RT)

←

16

0|| MS(EA,2).

234

lhzu RT, D(RA) Load halfword from EA = (RA|0) + EXTS(D) and pad left

with zeroes,

(RT) ←

16

0|| MS(EA,2).

Update the base address,

(RA)

← EA.

235

lhzux RT, RA, RB Load halfword from EA = (RA|0) + (RB) and pad left with

zeroes,

(RT)

←

16

0|| MS(EA,2).

Update the base address,

(RA) ← EA.

236

lhzx RT, RA, RB Load halfword from EA = (RA|0) + (RB) and pad left with

zeroes,

(RT)

←

16

0|| MS(EA,2).

237

li RT, IM Load immediate.

(RT)

← EXTS(IM)

Extended mnemonic for

addi RT,0,value

164

lis RT, IM Load immediate shifted.

(RT)

← (IM ||

16

0)

Extended mnemonic for

addis RT,0,value

167

lmw RT, D(RA) Load multiple words starting from EA = (RA|0) + EXTS(D).

Place into consecutive registers RT through GPR(31).

RA is not altered unless RA = GPR(31).

238

lswi RT, RA, NB Load consecutive bytes from EA=(RA|0).

Number of bytes n=32 if NB=0, else n=NB.

Stack bytes into words in CEIL(n/4)

consecutive registers starting with RT, to

R

FINAL

← ((RT + CEIL(n/4) – 1) % 32).

GPR(0) is consecutive to GPR(31).

RA is not altered unless RA = R

FINAL

.

239

lswx RT, RA, RB Load consecutive bytes from EA=(RA|0)+(RB).

Number of bytes n=XER[TBC].

Stack bytes into words in CEIL(n/4)

consecutive registers starting with RT, to

R

FINAL

← ((RT + CEIL(n/4) – 1) % 32).

GPR(0) is consecutive to GPR(31).

RA is not altered unless RA = R

FINAL

.

RB is not altered unless RB = R

FINAL

.

If n=0, content of RT is undefined.

241

lwarx RT, RA, RB Load word from EA = (RA|0) + (RB) and place in RT,

(RT) ← MS(EA,4).

Set the Reservation bit.

243

lwbrx RT, RA, RB Load word from EA = (RA|0) + (RB) then reverse byte

order,

(RT)

← MS(EA+3,1) || MS(EA+2,1) ||

MS(EA+1,1) || MS(EA,1).

244

lwz RT, D(RA) Load word from EA = (RA|0) + EXTS(D) and place in RT,

(RT) ← MS(EA,4).

245

Table A-1. PPC405 Instruction Syntax Summary (Continued)

Mnemonic Operands Function Other Registers Changed Page

Loading...

Loading...