376 AMCC Proprietary

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

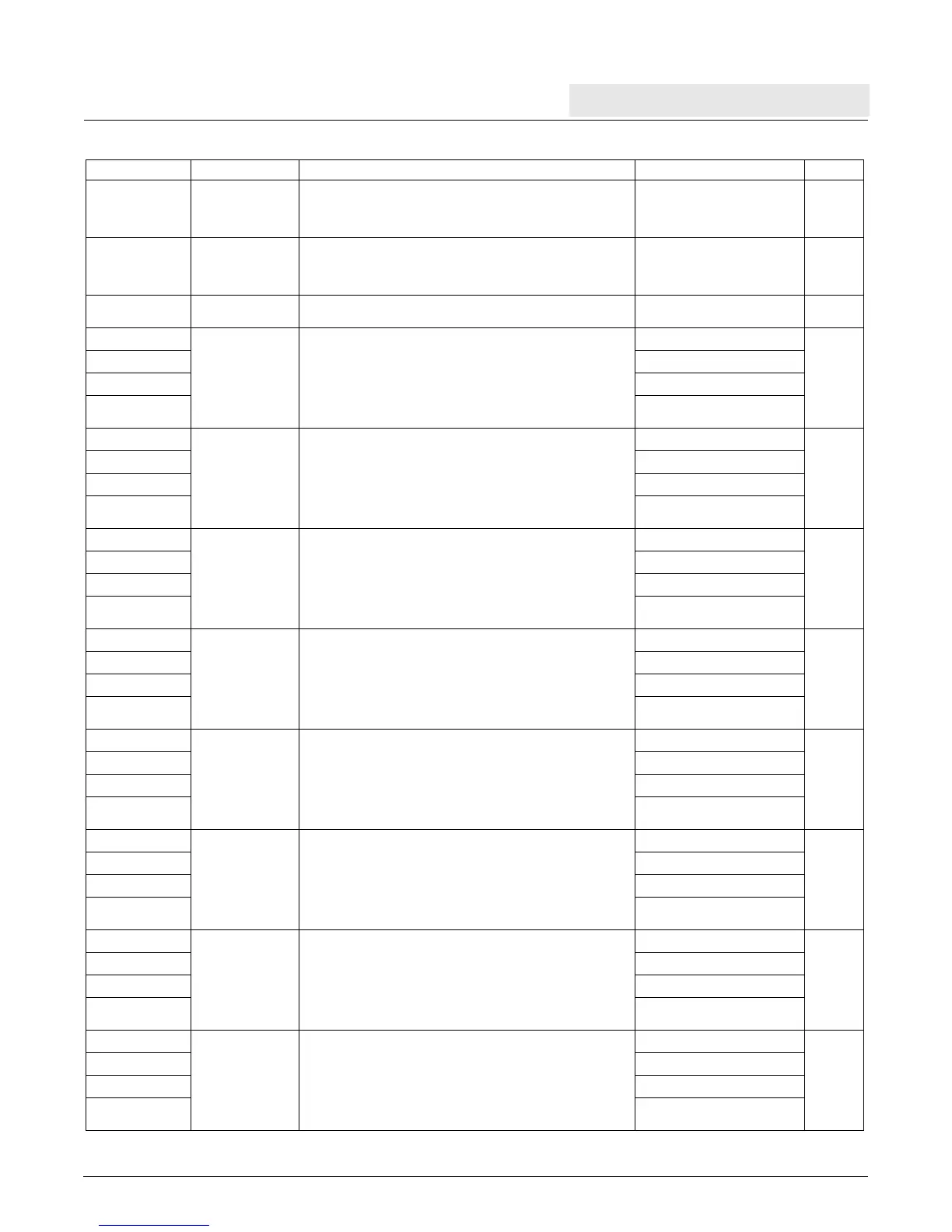

lwzu RT, D(RA) Load word from EA = (RA|0) + EXTS(D) and place in RT,

(RT)

← MS(EA,4).

Update the base address,

(RA)

← EA.

246

lwzux RT, RA, RB Load word from EA = (RA|0) + (RB) and place in RT,

(RT) ← MS(EA,4).

Update the base address,

(RA)

← EA.

247

lwzx RT, RA, RB Load word from EA = (RA|0) + (RB) and place in RT,

(RT)

← MS(EA,4).

248

macchw

RT, RA, RB prod

0:31

← (RA)

16:31

x (RB)

0:15

signed

temp

0:32

← prod

0:31

+ (RT)

(RT) ← temp

1:32

249

macchw.

CR[CR0]

macchwo

XER[SO, OV]

macchwo.

CR[CR0]

XER[SO, OV]

macchws

RT, RA, RB prod

0:31

← (RA)

16:31

x (RB)

0:15

signed

temp

0:32

← prod

0:31

+ (RT)

if ((prod

0

= RT

0

) ∧ (RT

0

≠ temp

1

)) then

(RT) ← (RT

0

||

31

(¬RT

0

))

else (RT)

← temp

1:32

250

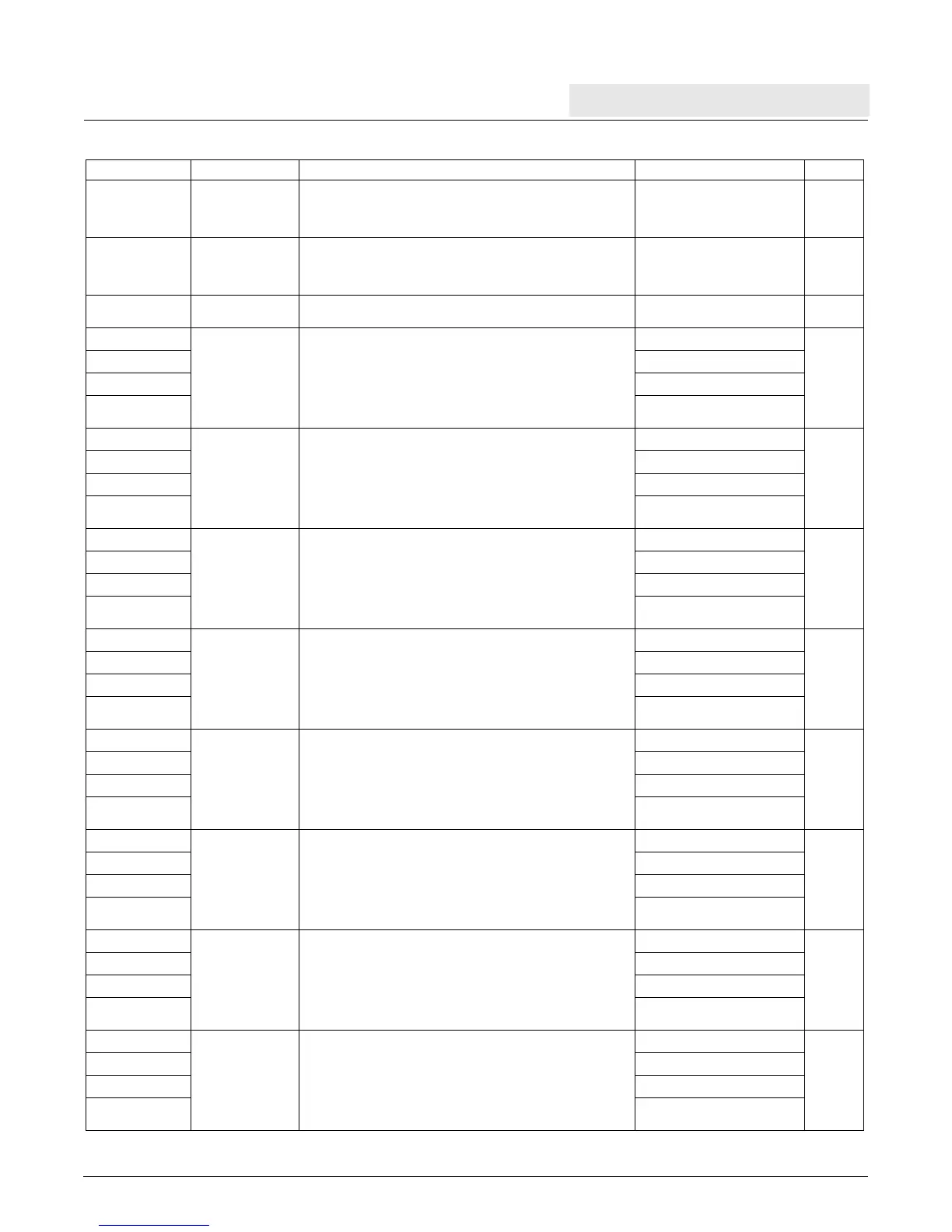

macchws.

CR[CR0]

macchwso

XER[SO, OV]

macchwso.

CR[CR0]

XER[SO, OV]

macchwsu

RT, RA, RB prod

0:31

← (RA)

16:31

x (RB)

0:15

unsigned

temp

0:32

← prod

0:31

+ (RT)

(RT) ← (temp

1:32

∨

32

temp

0

)

251

macchwsu.

CR[CR0]

macchwsuo

XER[SO, OV]

macchwsuo.

CR[CR0]

XER[SO, OV]

macchwu

RT, RA, RB prod

0:31

← (RA)

16:31

x (RB)

0:15

unsigned

temp

0:32

← prod

0:31

+ (RT)

(RT) ← temp

1:32

252

macchwu.

CR[CR0]

macchwuo

XER[SO, OV]

macchwuo.

CR[CR0]

XER[SO, OV]

machhw

RT, RA, RB prod

0:15

← (RA)

16:31

x (RB)

0:15

signed

temp

0:32

← prod

0:31

+ (RT)

(RT) ← temp

1:32

253

machhw.

CR[CR0]

machhwo

XER[SO, OV]

machhwo.

CR[CR0]

XER[SO, OV]

machhws

RT, RA, RB prod

0:31

← (RA)

0:15

x (RB)

0:15

signed

temp

0:32

← prod

0:31

+ (RT)

if ((prod

0

= RT

0

) ∧ (RT

0

≠ temp

1

)) then

(RT)

← (RT

0

||

31

(¬RT

0

))

else (RT)

← temp

1:32

254

machhws.

CR[CR0]

machhwso

XER[SO, OV]

machhwso.

CR[CR0]

XER[SO, OV]

machhwsu

RT, RA, RB prod

0:31

← (RA)

0:15

x (RB)

0:15

unsigned

temp

0:32

← prod

0:31

+ (RT)

(RT)

← (temp

1:32

∨

32

temp

0

)

255

machhwsu.

CR[CR0]

machhwsuo

XER[SO, OV]

machhwsuo.

CR[CR0]

XER[SO, OV]

machhwu

RT, RA, RB prod

0:31

← (RA)

0:15

x (RB)

0:15

unsigned

temp

0:32

← prod

0:31

+ (RT)

(RT)

← temp

1:32

256

machhwu.

CR[CR0]

machhwuo

XER[SO, OV]

machhwuo.

CR[CR0]

XER[SO, OV]

Table A-1. PPC405 Instruction Syntax Summary (Continued)

Mnemonic Operands Function Other Registers Changed Page

Loading...

Loading...