UM10375 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

User manual Rev. 3 — 14 June 2011 10 of 368

3.1 How to read this chapter

The system configuration registers apply to all LPC13xx parts with the following

exceptions:

USB clocking and power control

Since the USB block is available on the LPC1342 and LPC1343 only, the registers and

register bits listed in Table 4

are reserved for parts LPC1311 and LPC1313:

SSP1

The SSP1 block is available on the LPC1313FBD48/01 only. SSP1 related registers and

register bits are reserved for the following parts: LPC1311/13/42/43 and

LPC1311FHN33/01 and LPC1313FHN33/01.

BOD control

The number of programmable BOD levels for forced reset is different for the LPC1300 and

the LPC1300L series. See Table 5

. The BOD trip levels for the LPC1300 and LPC1300L

series are listed in the LPC1311/13/42/43 data sheet.

UM10375

Chapter 3: LPC13xx System configuration

Rev. 3 — 14 June 2011 User manual

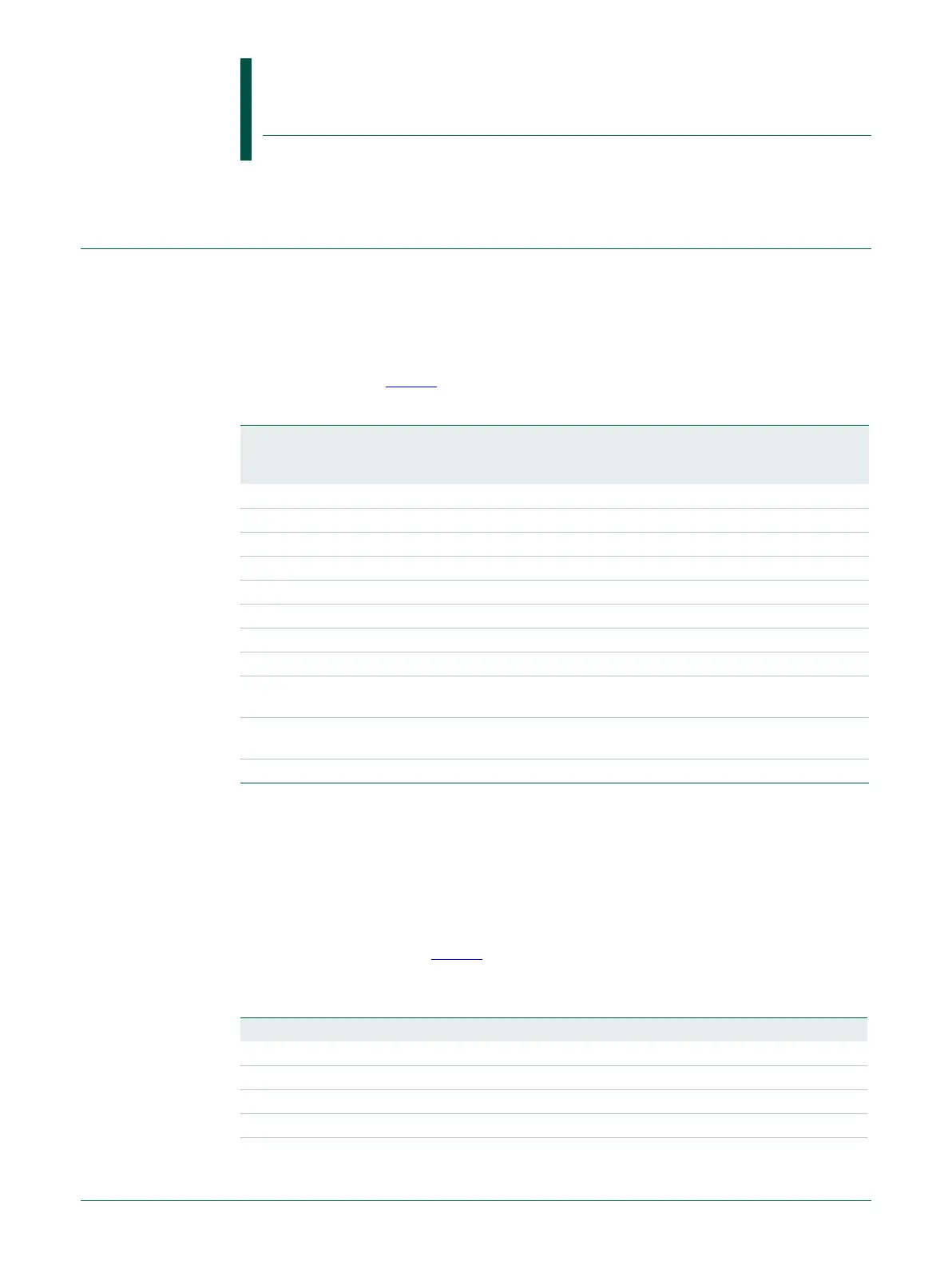

Table 4. USB related registers and register bits reserved for LPC1311/13

Name Access Address

offset

Description Register bits

reserved for

LPC1311/13

USBPLLCTRL R/W 0x010 USB PLL control all

USBPLLSTAT R 0x014 USB PLL status all

USBPLLCLKSEL R/W 0x048 USB PLL clock source select all

USBPLLCLKUEN R/W 0x04C USB PLL clock source update enable all

SYSAHBCLKCTRL R/W 0x080 System AHB clock control bit 14

USBCLKSEL R/W 0x0C0 USB clock source select all

USBCLKUEN R/W 0x0C4 USB clock source update enable all

USBCLKDIV R/W 0x0C8 USB clock source divider all

PDSLEEPCFG R/W 0x230 Power-down states in Deep-sleep

mode

bits 8 and 10

PDAWAKECFG R/W 0x234 Power-down states after wake-up from

Deep-sleep mode

bits 8 and 10

PDRUNCFG R/W 0x238 Power-down configuration register bits 8 and 10

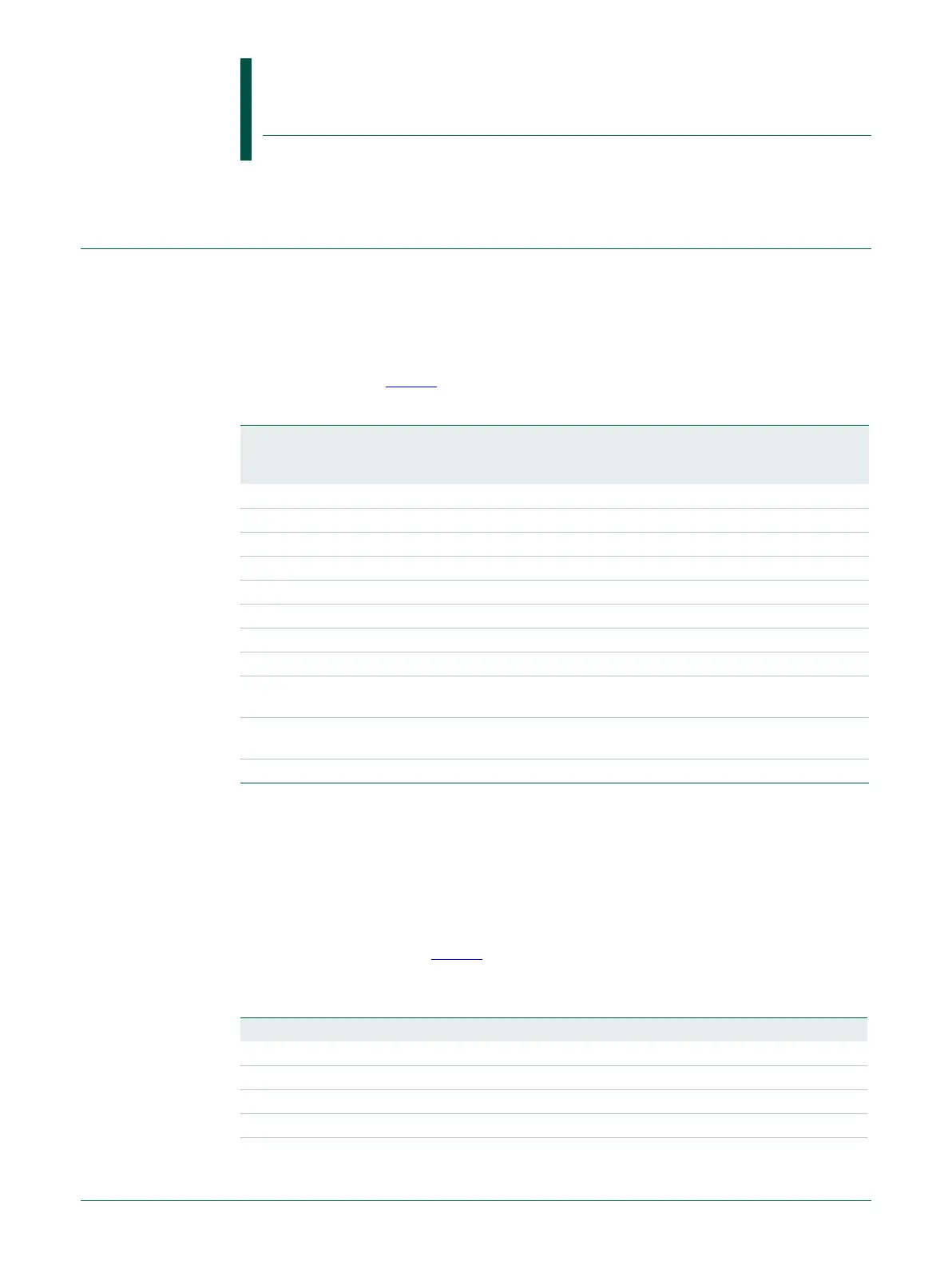

Table 5. BOD interrupt and reset levels

Series Type number Interrupt levels Reset levels

LPC1300 LPC1311FHN33 4 (programmable) 1 (fixed)

LPC1300 LPC1313FBD48 4 (programmable) 1 (fixed)

LPC1300 LPC1313FHN33 4 (programmable) 1 (fixed)

LPC1300 LPC1342FHN33 4 (programmable) 1 (fixed)

LPC1300 LPC1343FBD48 4 (programmable) 1 (fixed)

Loading...

Loading...