UM10375 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

User manual Rev. 3 — 14 June 2011 301 of 368

NXP Semiconductors

UM10375

Chapter 18: LPC13xx WatchDog Timer (WDT)

18.7 Register description

The Watchdog contains four registers as shown in Table 289 below.

[1] Reset Value reflects the data stored in used bits only. It does not include reserved bits content.

18.7.1 Watchdog Mode register (WDMOD - 0x4000 0000)

The WDMOD register controls the operation of the Watchdog through the combination of

WDEN and RESET bits. Note that a watchdog feed must be performed before any

changes to the WDMOD register take effect.

Once the WDEN and/or WDRESET bits are set they can not be cleared by software. Both

flags are cleared by reset or a Watchdog timer underflow.

WDTOF The Watchdog time-out flag is set when the Watchdog times out. This flag is

cleared by software or any reset except the WDT reset.

WDINT The Watchdog interrupt flag is set when the Watchdog times out. This flag is

cleared when any reset occurs. Once the watchdog interrupt is serviced, it can be

disabled in the NVIC or the watchdog interrupt request will be generated indefinitely. the

intent of the watchdog interrupt is to allow debugging watchdog activity without resetting

the device when the watchdog overflows.

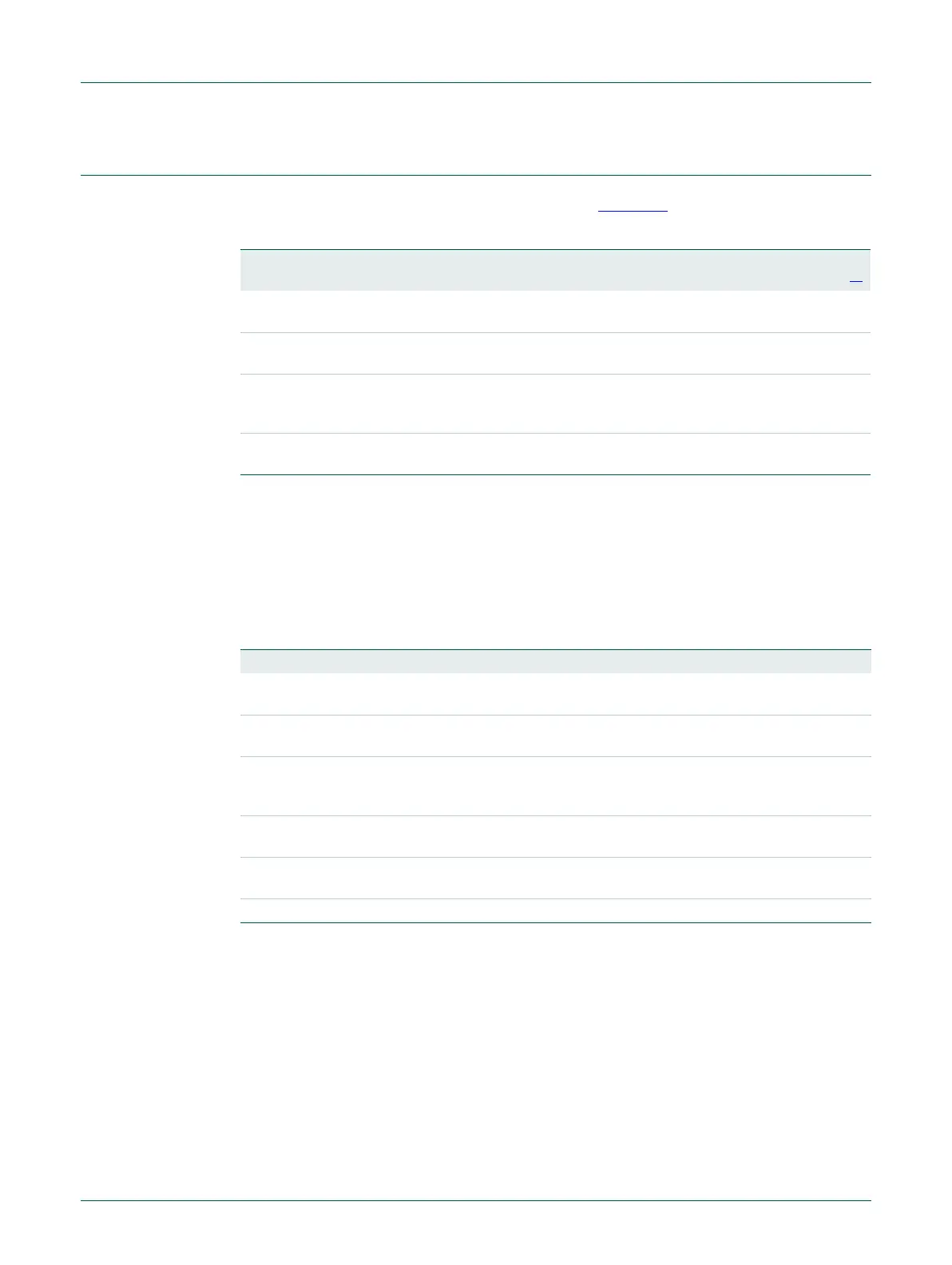

Table 289. Register overview: Watchdog timer (base address 0x4000 4000)

Name Access Address

offset

Description Reset

Value

[1]

WDMOD R/W 0x000 Watchdog mode register. This register contains the

basic mode and status of the Watchdog Timer.

0

WDTC R/W 0x004 Watchdog timer constant register. This register

determines the time-out value.

0xFF

WDFEED WO 0x008 Watchdog feed sequence register. Writing 0xAA

followed by 0x55 to this register reloads the

Watchdog timer with the value contained in WDTC.

NA

WDTV RO 0x00C Watchdog timer value register. This register reads

out the current value of the Watchdog timer.

0xFF

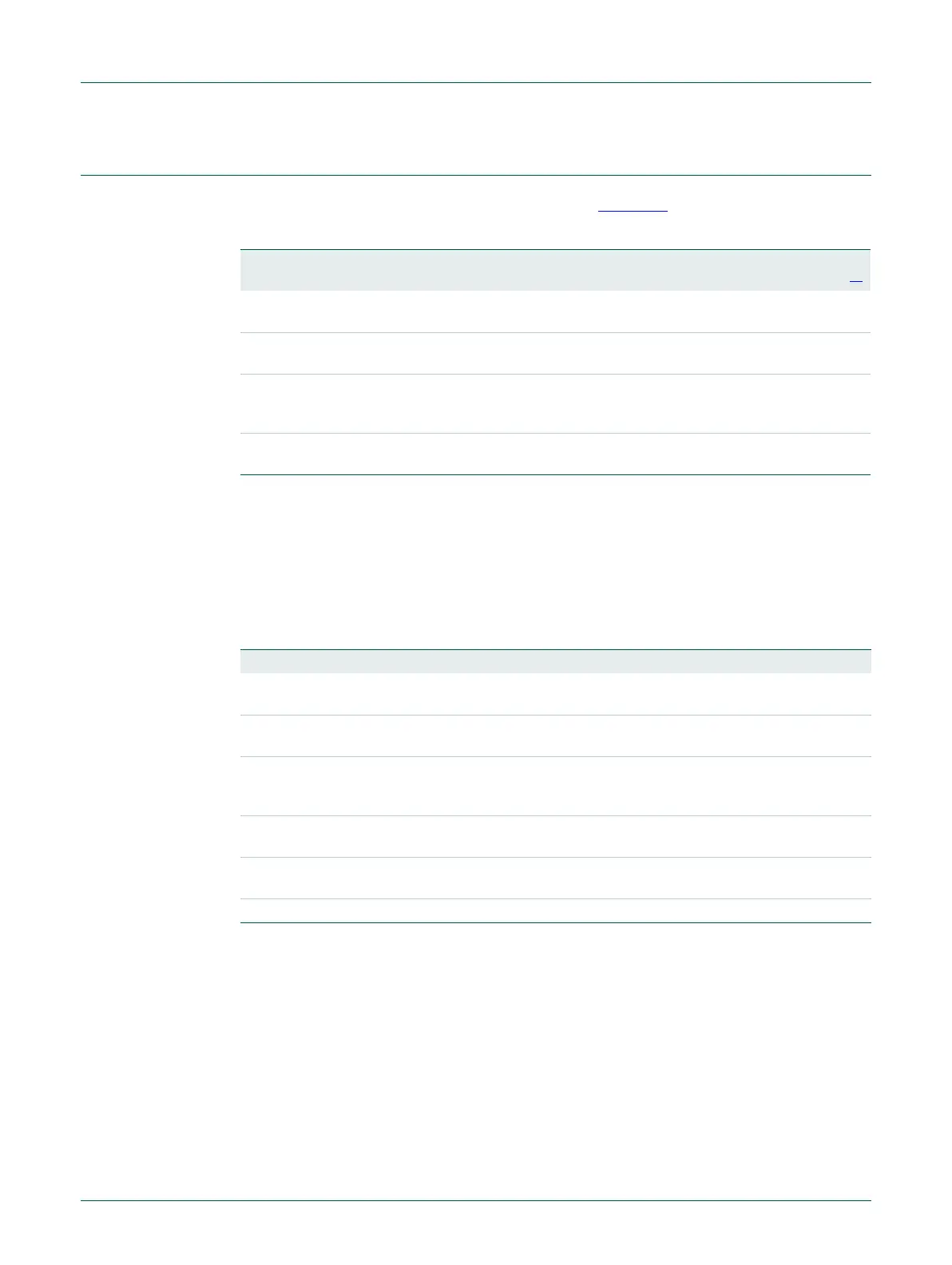

Table 290. Watchdog Mode register (WDMOD - address 0x4000 4000) bit description

Bit Symbol Description Reset Value

0 WDEN WDEN Watchdog enable bit (Set Only). When one, the

watchdog timer is running.

0

1 WDRESET WDRESET Watchdog reset enable bit (Set Only). When 1,

a watchdog time-out will cause a chip reset.

0

2 WDTOF WDTOF Watchdog time-out flag. Set when the watchdog

timer times out, cleared by software.

0 (After any

reset except

WDT)

3 WDINT WDINT Watchdog interrupt flag (Read Only, not clearable

by software).

0

7:4 - Reserved, user software should not write ones to reserved

bits. The value read from a reserved bit is not defined.

-

31:8 - reserved -

Loading...

Loading...