UM10375 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

User manual Rev. 3 — 14 June 2011 26 of 368

NXP Semiconductors

UM10375

Chapter 3: LPC13xx System configuration

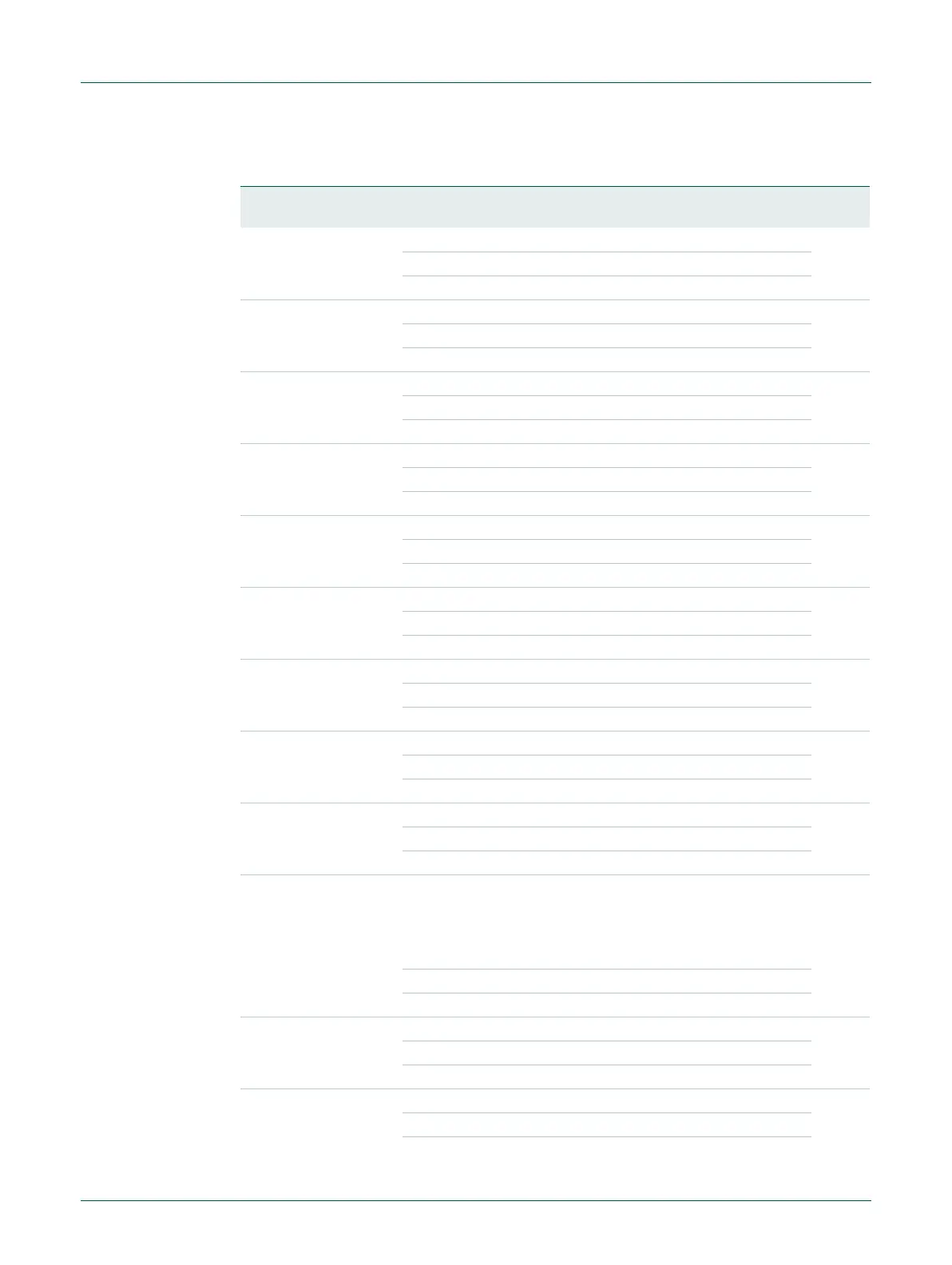

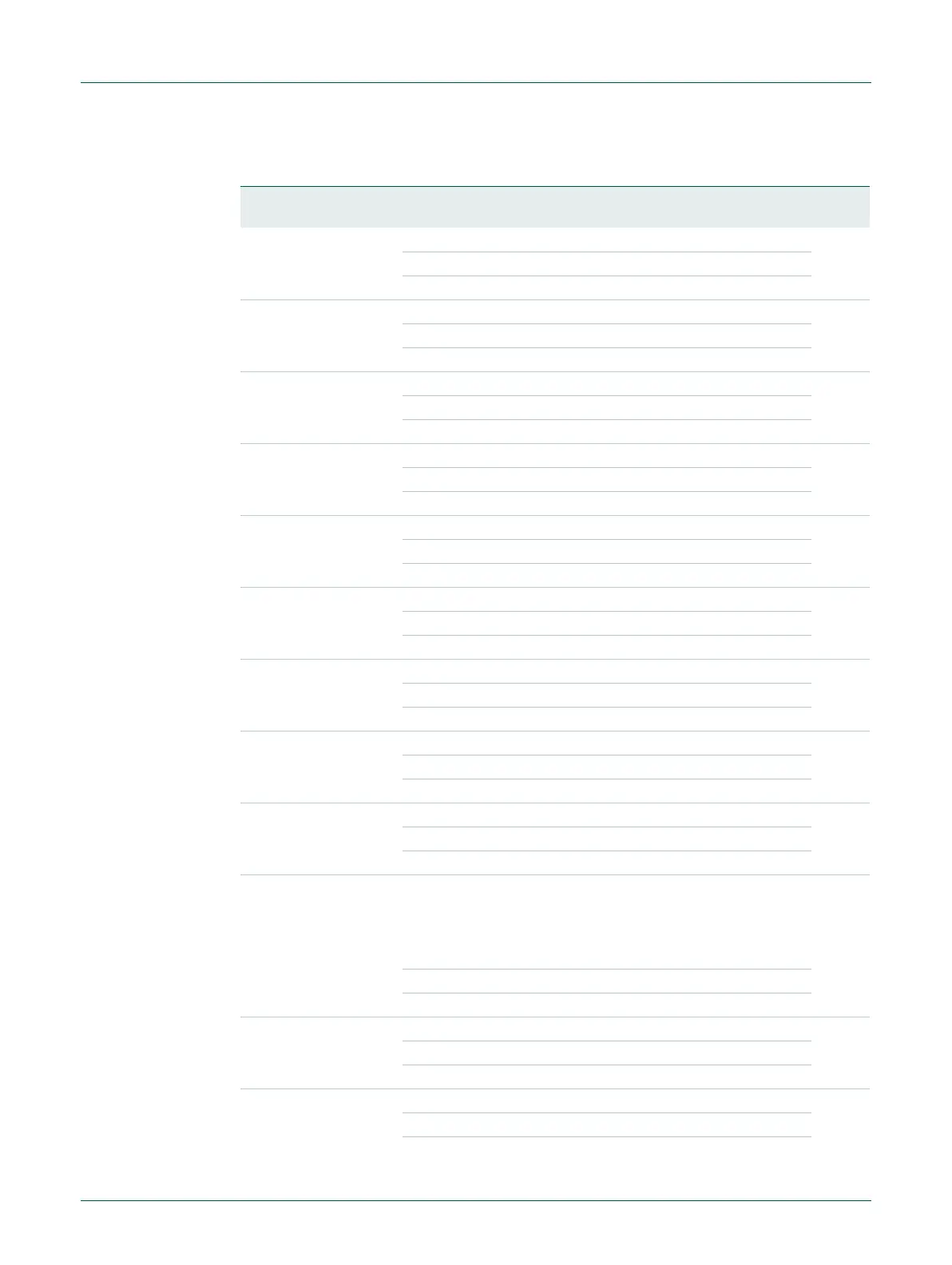

3 FLASHREG Enables clock for flash register interface. 1

0 Disabled

1 Enabled

4 FLASHARRAY Enables clock for flash array access. 1

0 Disabled

1 Enabled

5 I2C Enables clock for I2C. 0

0 Disabled

1 Enabled

6 GPIO Enables clock for GPIO. 1

0 Disabled

1 Enabled

7 CT16B0 Enables clock for 16-bit counter/timer 0. 0

0 Disabled

1 Enabled

8 CT16B1 Enables clock for 16-bit counter/timer 1. 0

0 Disabled

1 Enabled

9 CT32B0 Enables clock for 32-bit counter/timer 0. 0

0 Disabled

1 Enabled

10 CT32B1 Enables clock for 32-bit counter/timer 1. 0

0 Disabled

1 Enabled

11 SSP Enables clock for SSP. 1

0 Disabled

1 Enabled

12 UART Enables clock for UART. Note that for the

LPC1311/13/42/43, the UART pins must be configured

in the IOCON block before the UART clock can be

enabled. For the LPC1311/01 and LPC1313/01 no

special enabling sequence is required.

0

0 Disabled

1 Enabled

13 ADC Enables clock for ADC. 0

0 Disabled

1 Enabled

14 USB_REG Enables clock for USB_REG. 1

0 Disabled

1 Enabled

Table 25. System AHB clock control register (SYSAHBCLKCTRL, address 0x4004 8080) bit

description

…continued

Bit Symbol Value Description Reset

value

Loading...

Loading...