UM10375 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

User manual Rev. 3 — 14 June 2011 210 of 368

NXP Semiconductors

UM10375

Chapter 13: LPC13xx I2C-bus controller

[1] Reset value reflects the data stored in used bits only. It does not include reserved bits content.

13.8.1 I

2

C Control Set register (I2C0CONSET - 0x4000 0000)

The I2CONSET registers control setting of bits in the I2CON register that controls

operation of the I

2

C interface. Writing a one to a bit of this register causes the

corresponding bit in the I

2

C control register to be set. Writing a zero has no effect.

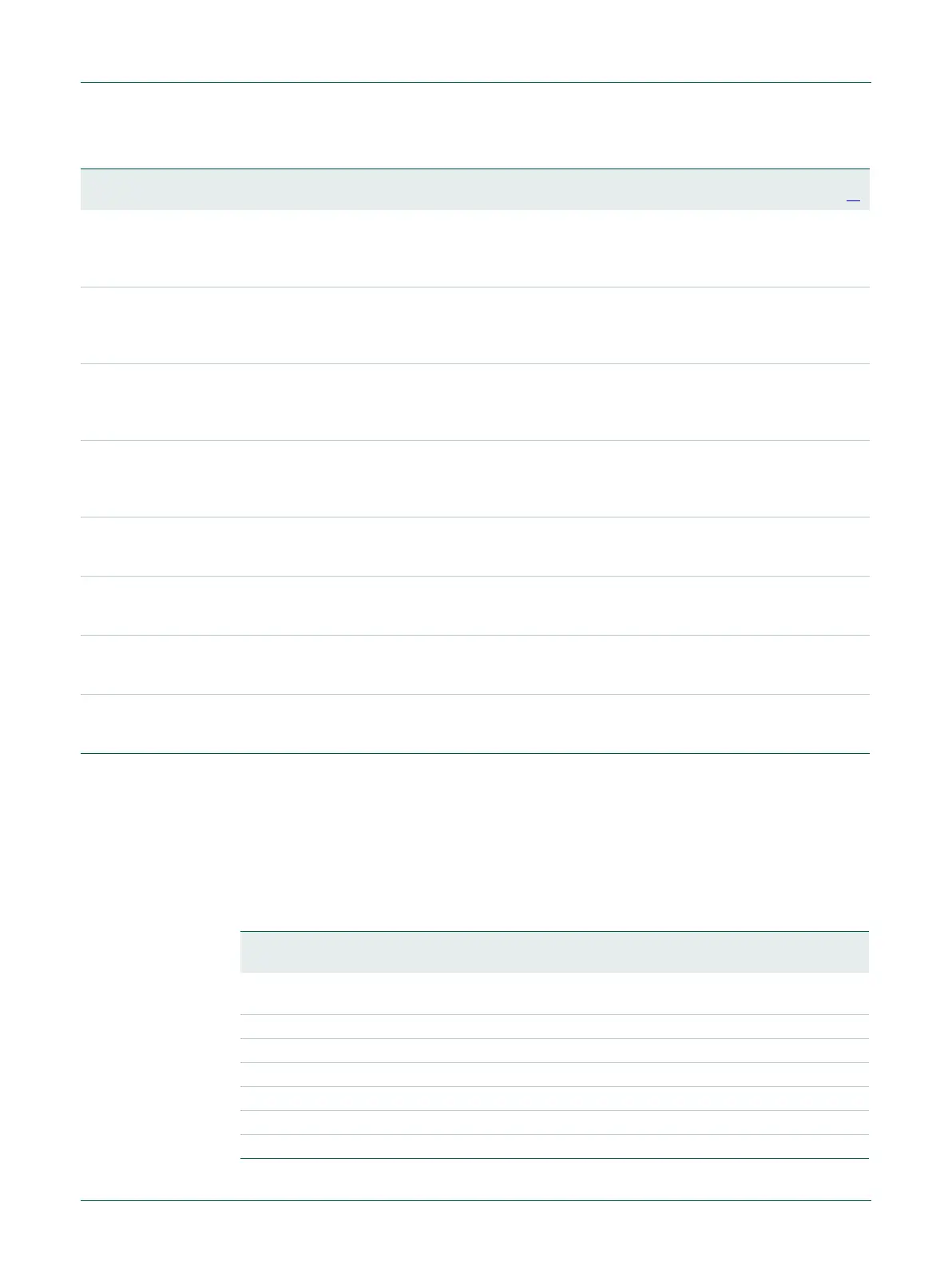

I2C0ADR1 R/W 0x020 I2C Slave Address Register 1. Contains the 7-bit slave address for

operation of the I

2

C interface in slave mode, and is not used in master

mode. The least significant bit determines whether a slave responds to

the General Call address.

0x00

I2C0ADR2 R/W 0x024 I2C Slave Address Register 2. Contains the 7-bit slave address for

operation of the I

2

C interface in slave mode, and is not used in master

mode. The least significant bit determines whether a slave responds to

the General Call address.

0x00

I2C0ADR3 R/W 0x028 I2C Slave Address Register 3. Contains the 7-bit slave address for

operation of the I

2

C interface in slave mode, and is not used in master

mode. The least significant bit determines whether a slave responds to

the General Call address.

0x00

I2C0DATA_

BUFFER

RO 0x02C Data buffer register. The contents of the 8 MSBs of the I2DAT shift

register will be transferred to the DATA_BUFFER automatically after

every nine bits (8 bits of data plus ACK or NACK) has been received on

the bus.

0x00

I2C0MASK0 R/W 0x030 I2C Slave address mask register 0. This mask register is associated

with I2ADR0 to determine an address match. The mask register has no

effect when comparing to the General Call address (‘0000000’).

0x00

I2C0MASK1 R/W 0x034 I2C Slave address mask register 1. This mask register is associated

with I2ADR0 to determine an address match. The mask register has no

effect when comparing to the General Call address (‘0000000’).

0x00

I2C0MASK2 R/W 0x038 I2C Slave address mask register 2. This mask register is associated

with I2ADR0 to determine an address match. The mask register has no

effect when comparing to the General Call address (‘0000000’).

0x00

I2C0MASK3 R/W 0x03C I2C Slave address mask register 3. This mask register is associated

with I2ADR0 to determine an address match. The mask register has no

effect when comparing to the General Call address (‘0000000’).

0x00

Table 216. Register overview: I

2

C (base address 0x4000 0000) …continued

Name Access Address

offset

Description Reset

value

[1]

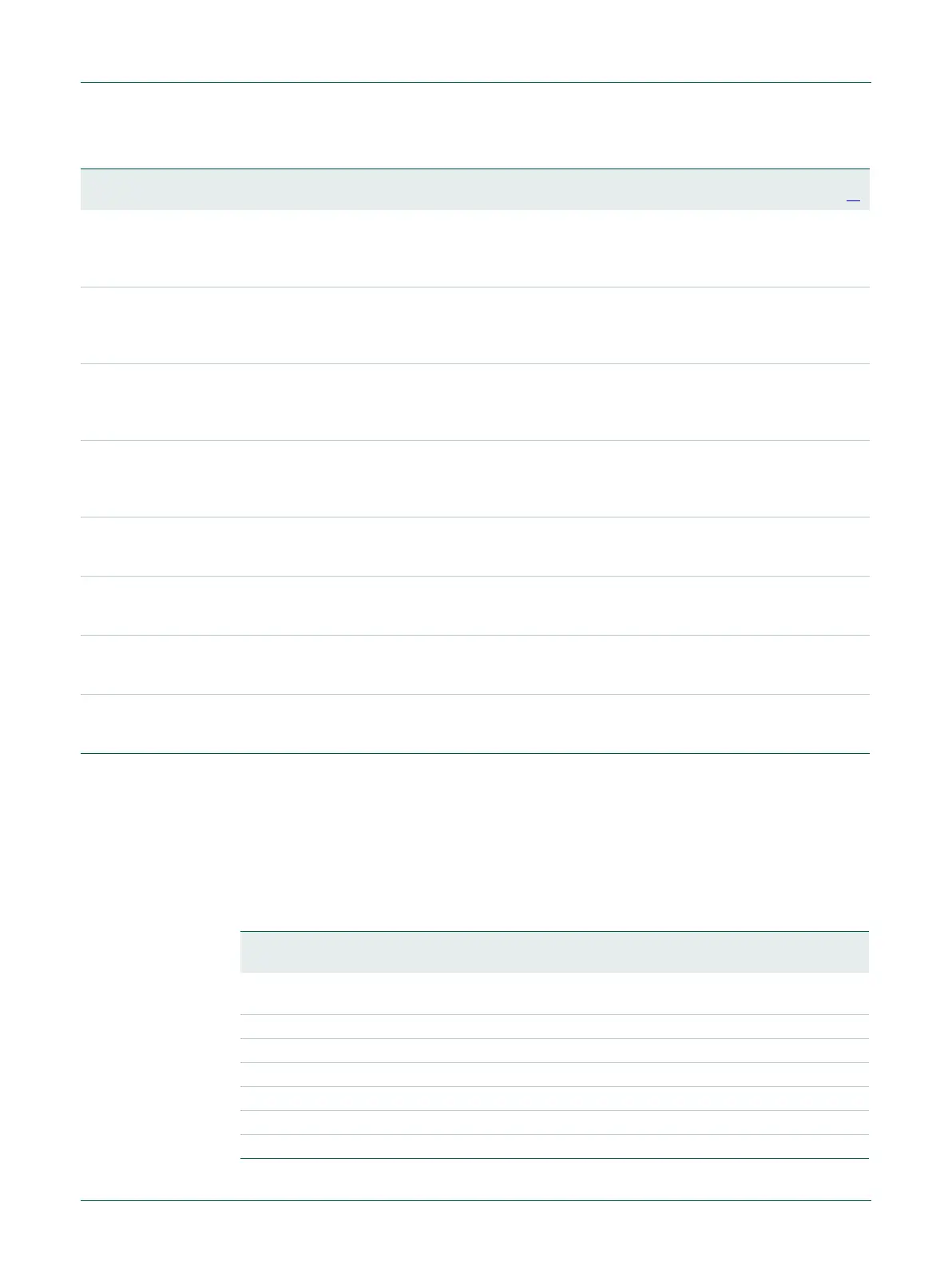

Table 217. I

2

C Control Set register (I2C0CONSET - address 0x4000 0000) bit description

Bit Symbol Description Reset

value

1:0 - Reserved. User software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

2 AA Assert acknowledge flag.

3SI I

2

C interrupt flag. 0

4 STO STOP flag. 0

5 STA START flag. 0

6I2EN I

2

C interface enable. 0

31:7 - Reserved. The value read from a reserved bit is not defined. -

Loading...

Loading...