UM10375 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

User manual Rev. 3 — 14 June 2011 214 of 368

NXP Semiconductors

UM10375

Chapter 13: LPC13xx I2C-bus controller

I2SCLL and I2SCLH values should not necessarily be the same. Software can set

different duty cycles on SCL by setting these two registers. For example, the I

2

C-bus

specification defines the SCL low time and high time at different values for a Fast-mode

and Fast-mode Plus I

2

C.

13.8.6 I

2

C Control Clear register (I2C0CONCLR - 0x4000 0018)

The I2CONCLR registers control clearing of bits in the I2CON register that controls

operation of the I

2

C interface. Writing a one to a bit of this register causes the

corresponding bit in the I

2

C control register to be cleared. Writing a zero has no effect.

AAC is the Assert Acknowledge Clear bit. Writing a 1 to this bit clears the AA bit in the

I2CONSET register. Writing 0 has no effect.

SIC is the I

2

C Interrupt Clear bit. Writing a 1 to this bit clears the SI bit in the I2CONSET

register. Writing 0 has no effect.

STAC is the START flag Clear bit. Writing a 1 to this bit clears the STA bit in the

I2CONSET register. Writing 0 has no effect.

I2ENC is the I

2

C Interface Disable bit. Writing a 1 to this bit clears the I2EN bit in the

I2CONSET register. Writing 0 has no effect.

13.8.7 I

2

C Monitor mode control register (I2C0MMCTRL - 0x4000 001C)

This register controls the Monitor mode which allows the I

2

C module to monitor traffic on

the I

2

C bus without actually participating in traffic or interfering with the I

2

C bus.

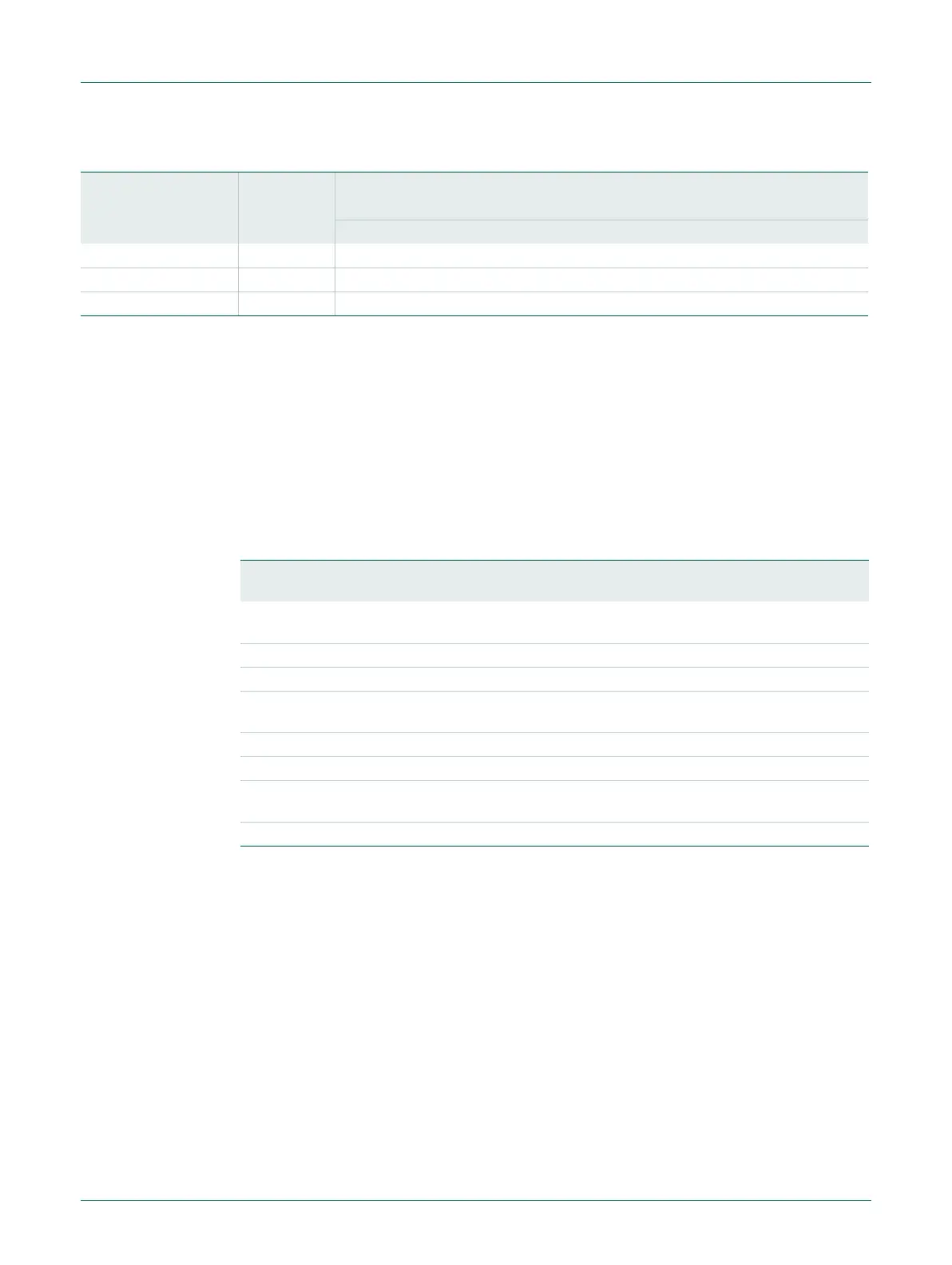

Table 223. I2SCLL + I2SCLH values for selected I

2

C clock values

I

2

C mode I

2

C bit

frequency

PCLK_I2C (MHz)

6 8 10 12 16 20 30 40 50 60 70

I2SCLH + I2SCLL

Standard mode 100 kHz 60 80 100 120 160 200 300 400 500 600 700

Fast-mode 400 kHz 15 20 25 30 40 50 75 100 125 150 175

Fast-mode Plus 1 MHz - 8 10 12 16 20 30 40 50 60 70

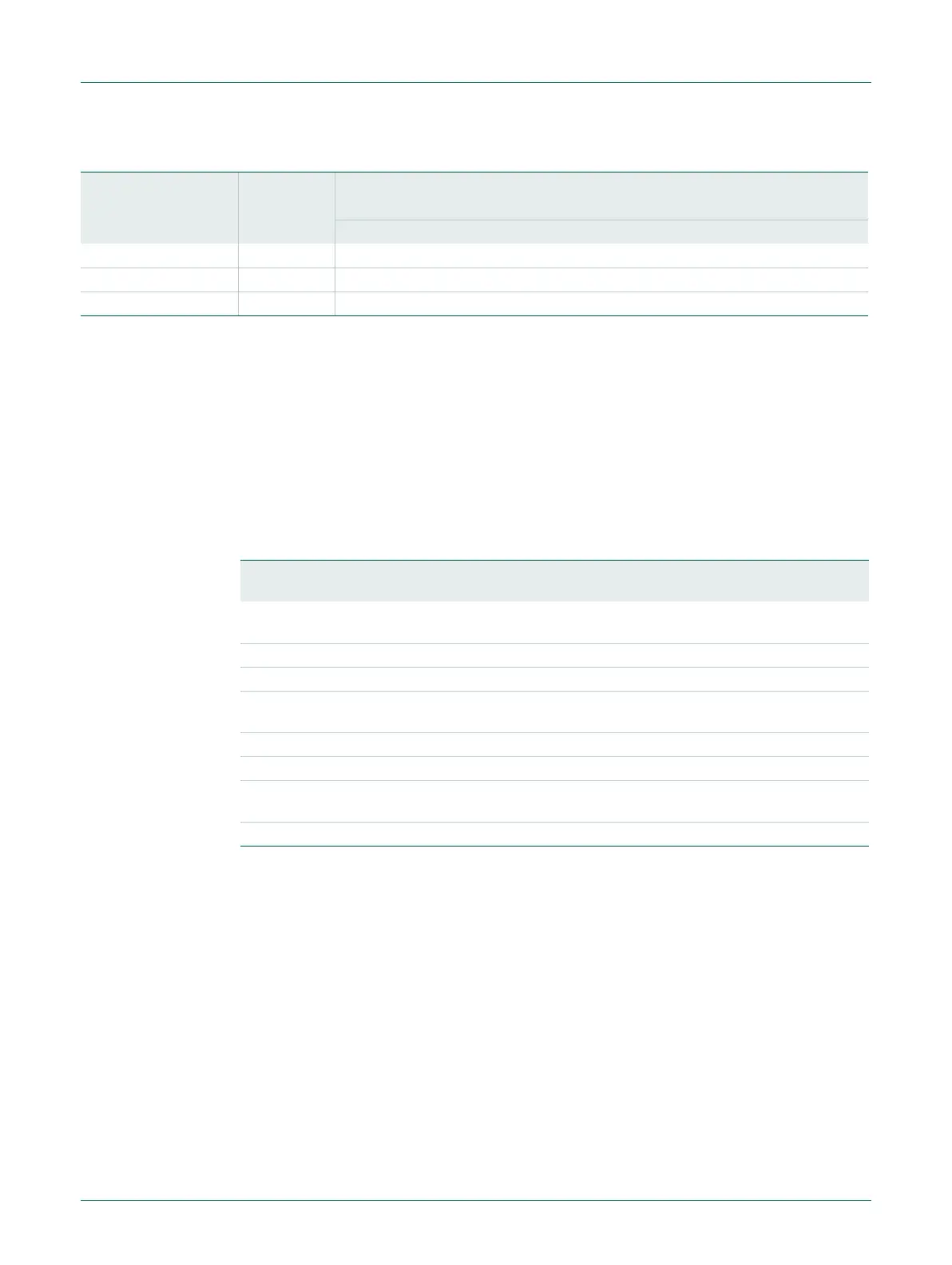

Table 224. I

2

C Control Clear register (I2C0CONCLR - 0x4000 0018) bit description

Bit Symbol Description Reset

value

1:0 - Reserved. User software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

2 AAC Assert acknowledge Clear bit.

3SIC I

2

C interrupt Clear bit. 0

4 - Reserved. User software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

5 STAC START flag Clear bit. 0

6I2ENCI

2

C interface Disable bit. 0

7 - Reserved. User software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

31:8 - Reserved. The value read from a reserved bit is not defined. -

Loading...

Loading...