UM10375 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

User manual Rev. 3 — 14 June 2011 69 of 368

NXP Semiconductors

UM10375

Chapter 6: LPC13xx Interrupt controller

6.6.4 Interrupt Clear-Enable Register 1 register

The ICER1 register allows disabling the second group of peripheral interrupts, or for

reading the enabled state of those interrupts. Enabling interrupts is done through the

ISER0 and ISER1 registers (Section 6.6.1

and Section 6.6.2).

The bit description is as follows for all bits in this register:

Write — Writing 0 has no effect, writing 1 disables the interrupt.

Read — 0 indicates that the interrupt is disabled, 1 indicates that the interrupt is enabled.

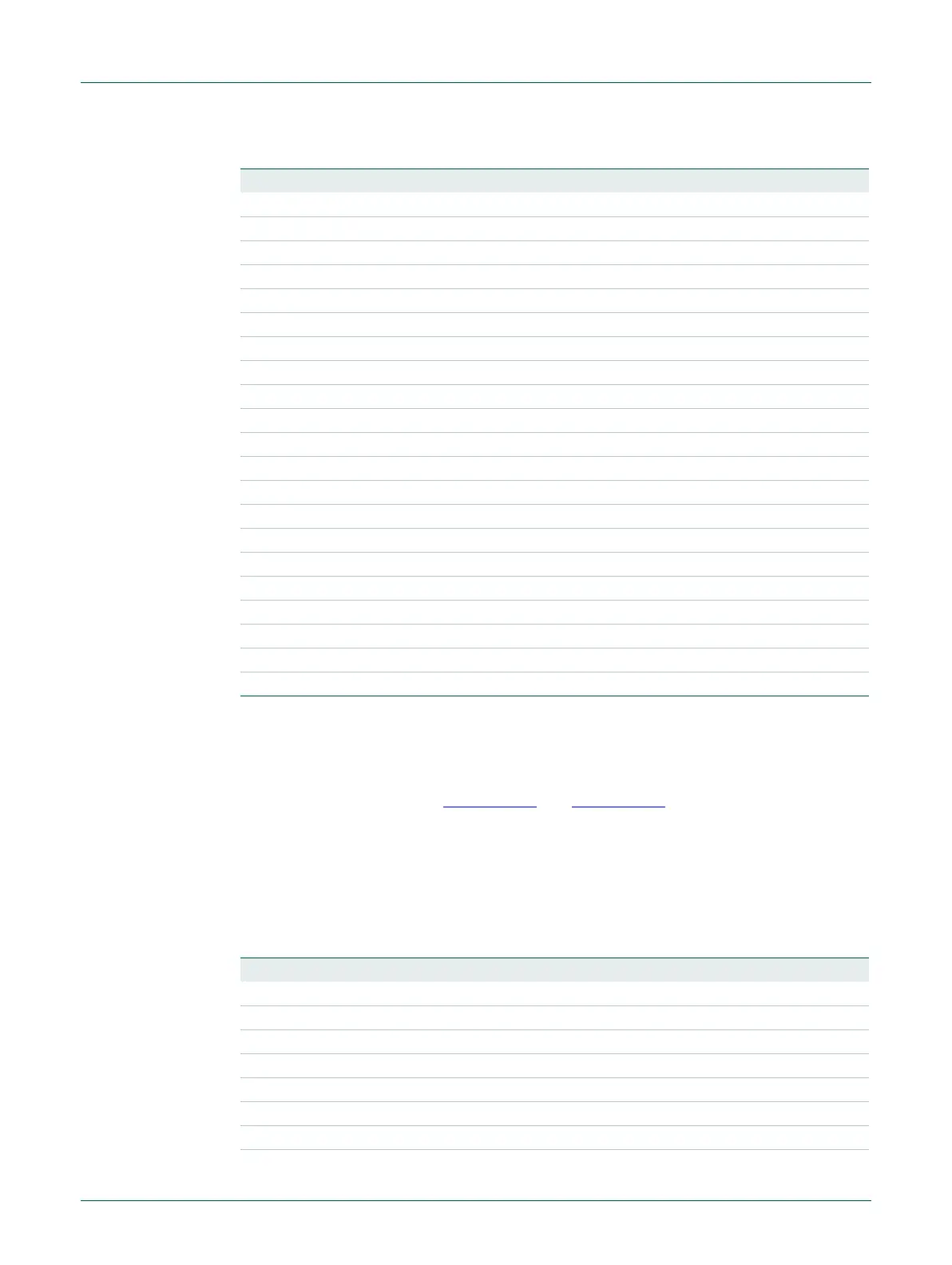

11 ICE_PIO0_11 PIO0_11 start logic input interrupt disable.

12 ICE_PIO1_0 PIO1_0 start logic input interrupt disable.

13 ICE_PIO1_1 PIO1_1 start logic input interrupt disable.

14 ICE_PIO1_2 PIO1_2 start logic input interrupt disable.

15 ICE_PIO1_3 PIO1_3 start logic input interrupt disable.

16 ICE_PIO1_4 PIO1_4 start logic input interrupt disable.

17 ICE_PIO1_5 PIO1_5 start logic input interrupt disable.

18 ICE_PIO1_6 PIO1_6 start logic input interrupt disable.

19 ICE_PIO1_7 PIO1_7 start logic input interrupt disable.

20 ICE_PIO1_8 PIO1_8 start logic input interrupt disable.

21 ICE_PIO1_9 PIO1_9 start logic input interrupt disable.

22 ICE_PIO1_10 PIO1_10 start logic input interrupt disable.

23 ICE_PIO1_11 PIO1_11 start logic input interrupt disable.

24 ICE_PIO2_0 PIO2_0 start logic input interrupt disable.

25 ICE_PIO2_1 PIO2_1 start logic input interrupt disable.

26 ICE_PIO2_2 PIO2_2 start logic input interrupt disable.

27 ICE_PIO2_3 PIO2_3 start logic input interrupt disable.

28 ICE_PIO2_4 PIO2_4 start logic input interrupt disable.

29 ICE_PIO2_5 PIO2_5 start logic input interrupt disable.

30 ICE_PIO2_6 PIO2_6 start logic input interrupt disable.

31 ICE_PIO2_7 PIO2_7 start logic input interrupt disable.

Table 70. Interrupt Clear-Enable Register 0

…continued

Bit Symbol Description

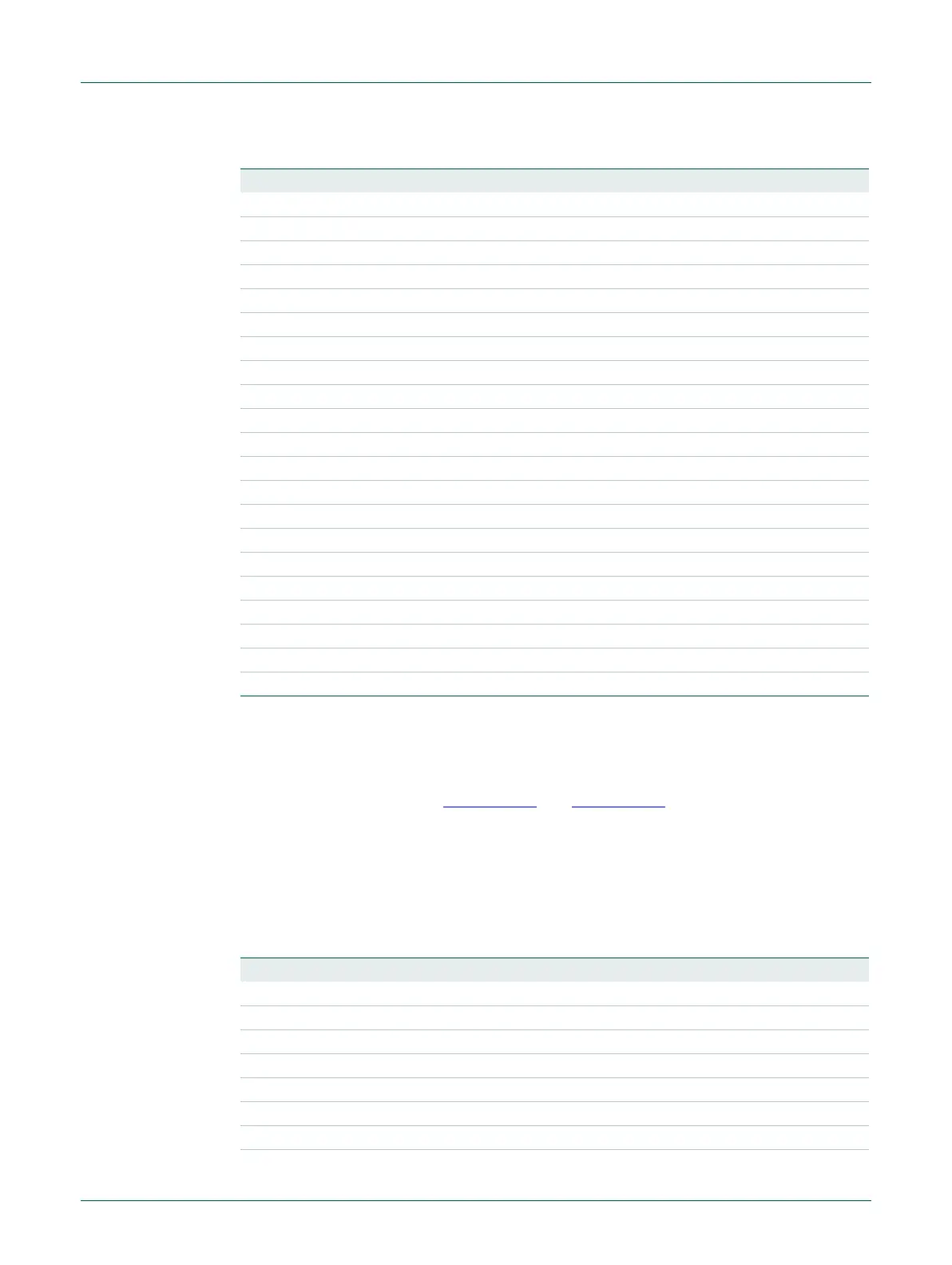

Table 71. Interrupt Clear-Enable Register 1 register (ICER1 - address 0xE000 E184) bit

description

Bit Symbol Description

0 ICE_PIO2_8 PIO0_0 start logic input interrupt disable.

1 ICE_PIO2_9 PIO2_9 start logic input interrupt disable.

2 ICE_PIO2_10 PIO2_10 start logic input interrupt disable.

3 ICE_PIO2_11 PIO2_11 start logic input interrupt disable.

4 ICE_PIO3_0 PIO3_0 start logic input interrupt disable.

5 ICE_PIO3_1 PIO3_0 start logic input interrupt disable.

6 ICE_PIO3_2 PIO3_0 start logic input interrupt disable.

7 ICE_PIO3_3 PIO3_0 start logic input interrupt disable.

Loading...

Loading...