UM10375 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

User manual Rev. 3 — 14 June 2011 70 of 368

NXP Semiconductors

UM10375

Chapter 6: LPC13xx Interrupt controller

6.6.5 Interrupt Set-Pending Register 0 register

The ISPR0 register allows setting the pending state of the first 32 peripheral interrupts, or

for reading the pending state of those interrupts. The remaining interrupts can have their

pending state set via the ISPR1 register (Section 6.6.6

). Clearing the pending state of

interrupts is done through the ICPR0 and ICPR1 registers (Section 6.6.7

and

Section 6.6.8

).

The bit description is as follows for all bits in this register:

Write — Writing 0 has no effect, writing 1 changes the interrupt state to pending.

Read — 0 indicates that the interrupt is not pending, 1 indicates that the interrupt is

pending.

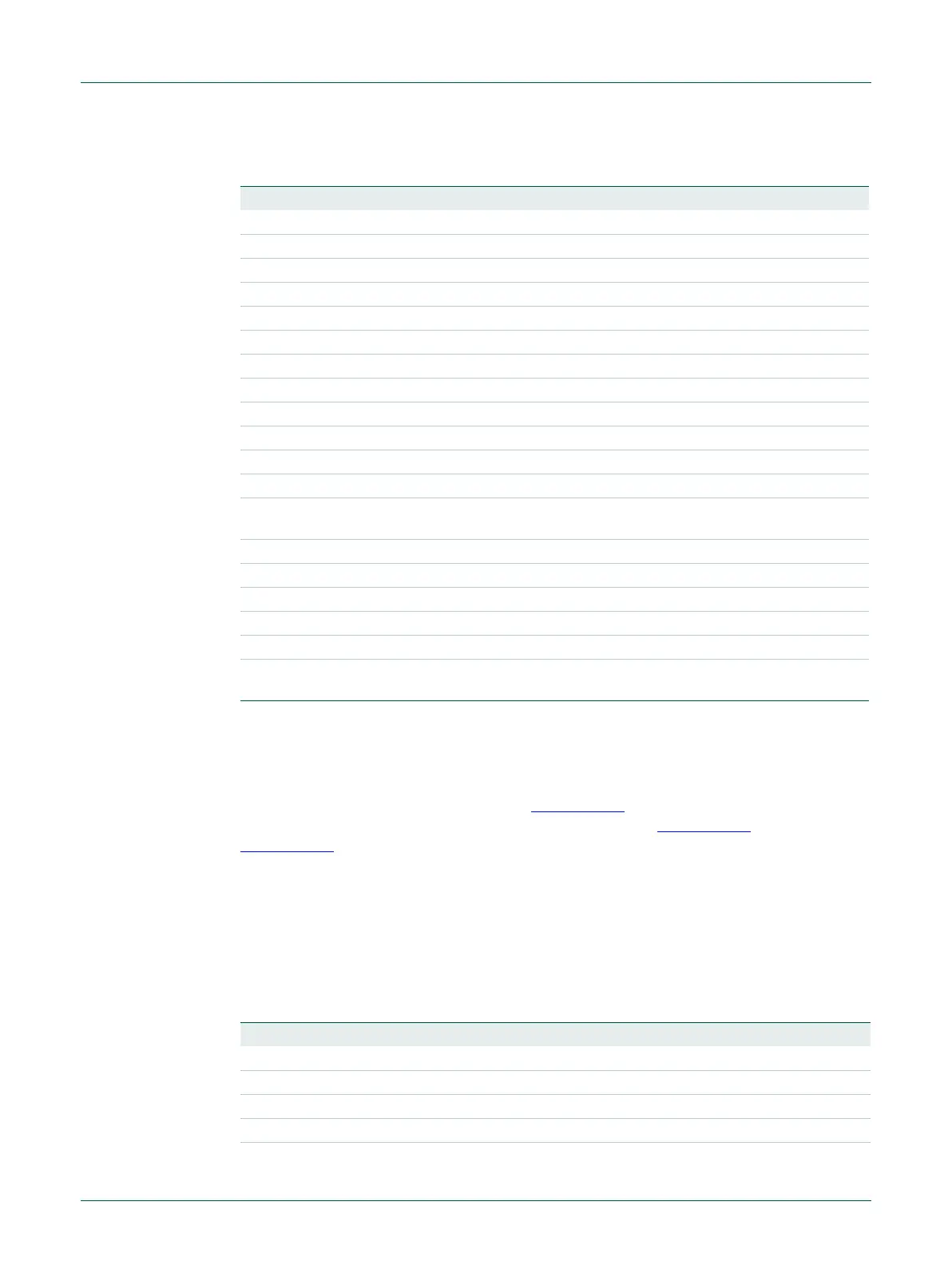

8 ICE_I2C0 I

2

C0 interrupt disable.

9 ICE_CT16B0 Timer CT16B0 interrupt disable.

10 ICE_CT16B1 Timer CT16B1 interrupt disable.

11 ICE_CT32B0 Timer CT32B0 interrupt disable.

12 ICE_CT32B1 Timer CT32B1 interrupt disable.

13 ICE_SSP0 SSP0 interrupt disable.

14 ICE_UART UART interrupt disable.

15 ICE_USBIRQ USB IRQ interrupt disable.

16 ICE_USBFRQ USB FRQ interrupt disable.

17 ICE_ADC ADC interrupt disable.

18 ICE_WDT WDT interrupt disable.

19 ICE_BOD BOD interrupt disable.

20 - Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

21 ICE_PIO_3 GPIO port 3 interrupt disable.

22 ICE_PIO_2 GPIO port 2 interrupt disable.

23 ICE_PIO_1 GPIO port 1 interrupt disable.

24 ICE_PIO_0 GPIO port 0 interrupt disable.

25 ICE_SSP1 SSP1 interrupt disable.

31:26 - Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

Table 71. Interrupt Clear-Enable Register 1 register (ICER1 - address 0xE000 E184) bit

description

…continued

Bit Symbol Description

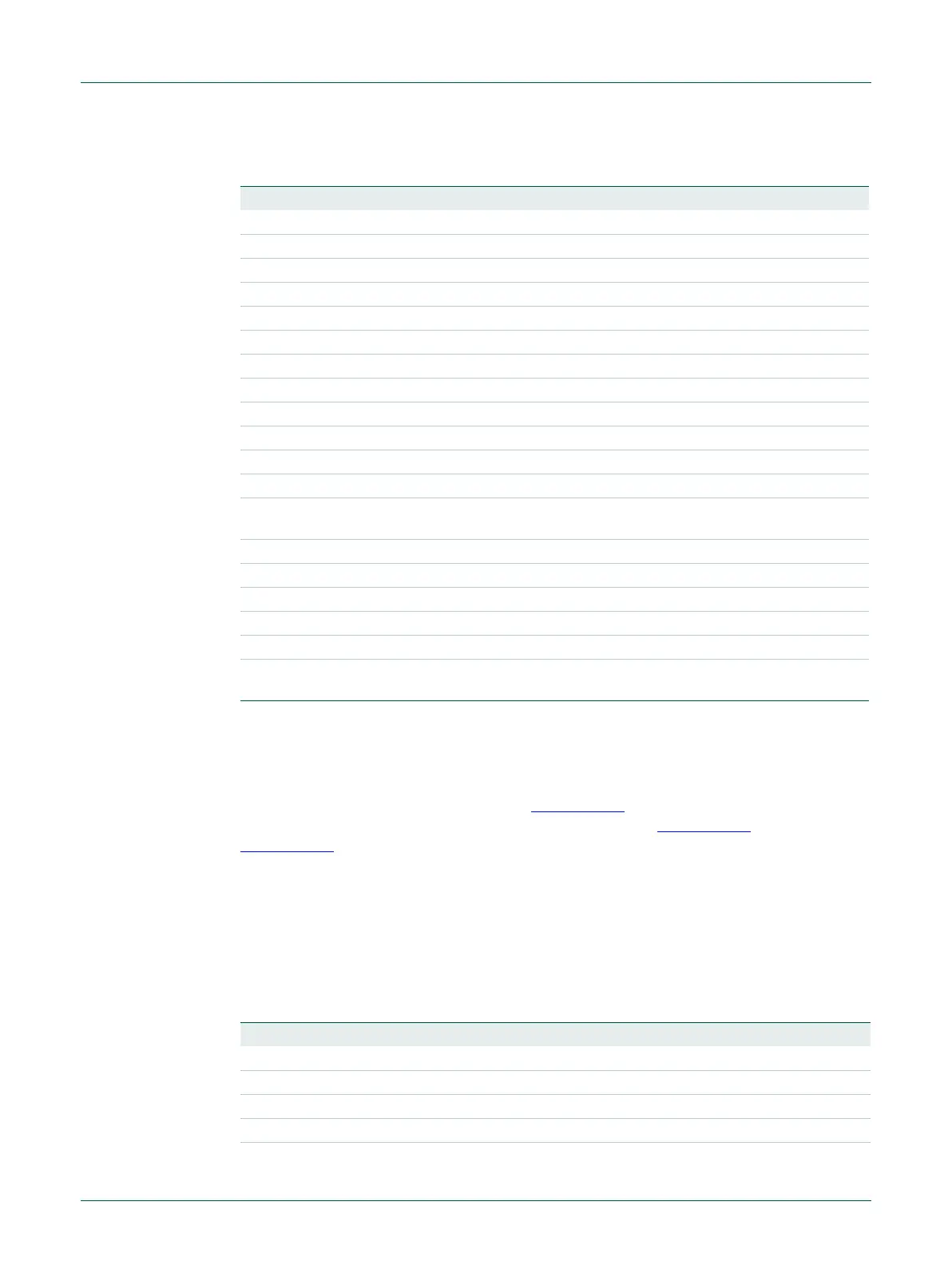

Table 72. Interrupt Set-Pending Register 0 register (ISPR0 - address 0xE000 E200) bit

description

Bit Symbol Description

0 ISP_PIO0_0 PIO0_0 start logic input interrupt pending set.

1 ISP_PIO0_1 PIO0_1 start logic input interrupt pending set.

2 ISP_PIO0_2 PIO0_2 start logic input interrupt pending set.

3 ISP_PIO0_3 PIO0_3 start logic input interrupt pending set.

4 ISP_PIO0_4 PIO0_4 start logic input interrupt pending set.

Loading...

Loading...