UM10375 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

User manual Rev. 3 — 14 June 2011 252 of 368

NXP Semiconductors

UM10375

Chapter 14: LPC13xx SSP0/1

14.6 Clocking and power control

The clocks and power to the SSP0 and SSP1 blocks are controlled by the following

registers:

1. The SSP0/1 block can be enabled or disabled through the SYSAHBCLKCTRL

register (see Table 25

).

2. The SSP0/1_PCLK are enabled in the SSP0 and SSP1 clock divider registers (see

Table 26

and Table 28). This clock is used by the SSP clock prescaler (Table 247).

Remark: Before accessing the SSP block, ensure that the SSP0/1_RST_N bits (bit 0 and

bit 2) in the PRESETCTRL register (Table 9

) are set to 1. This de-asserts the reset signal

to the SSP block.

14.7 Register description

The register addresses of the SSP0/1 controllers are shown in Table 241.

[1] Reset value reflects the data stored in used bits only. It does not include reserved bits content.

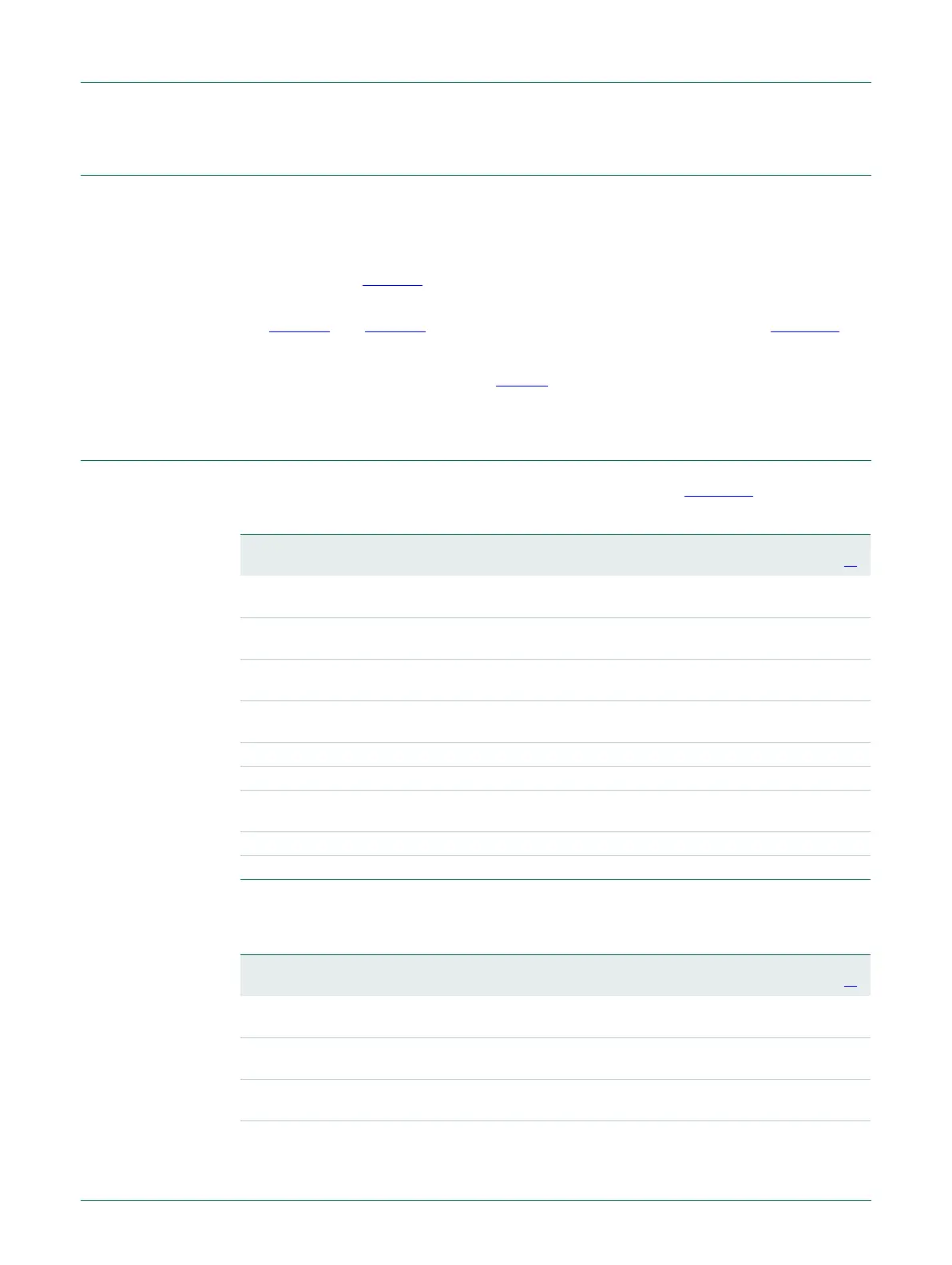

Table 241. Register overview: SSP0 (base address 0x4004 0000)

Name Access Address

offset

Description Reset

value

[1]

SSP0CR0 R/W 0x000 Control Register 0. Selects the serial clock rate,

bus type, and data size.

0

SSP0CR1 R/W 0x004 Control Register 1. Selects master/slave and

other modes.

0

SSP0DR R/W 0x008 Data Register. Writes fill the transmit FIFO, and

reads empty the receive FIFO.

0

SSP0SR RO 0x00C Status Register. 0x0000

0003

SSP0CPSR R/W 0x010 Clock Prescale Register. 0

SSP0IMSC R/W 0x014 Interrupt Mask Set and Clear Register. 0

SSP0RIS RO 0x018 Raw Interrupt Status Register. 0x0000

0008

SSP0MIS RO 0x01C Masked Interrupt Status Register. 0

SSP0ICR WO 0x020 SSPICR Interrupt Clear Register. NA

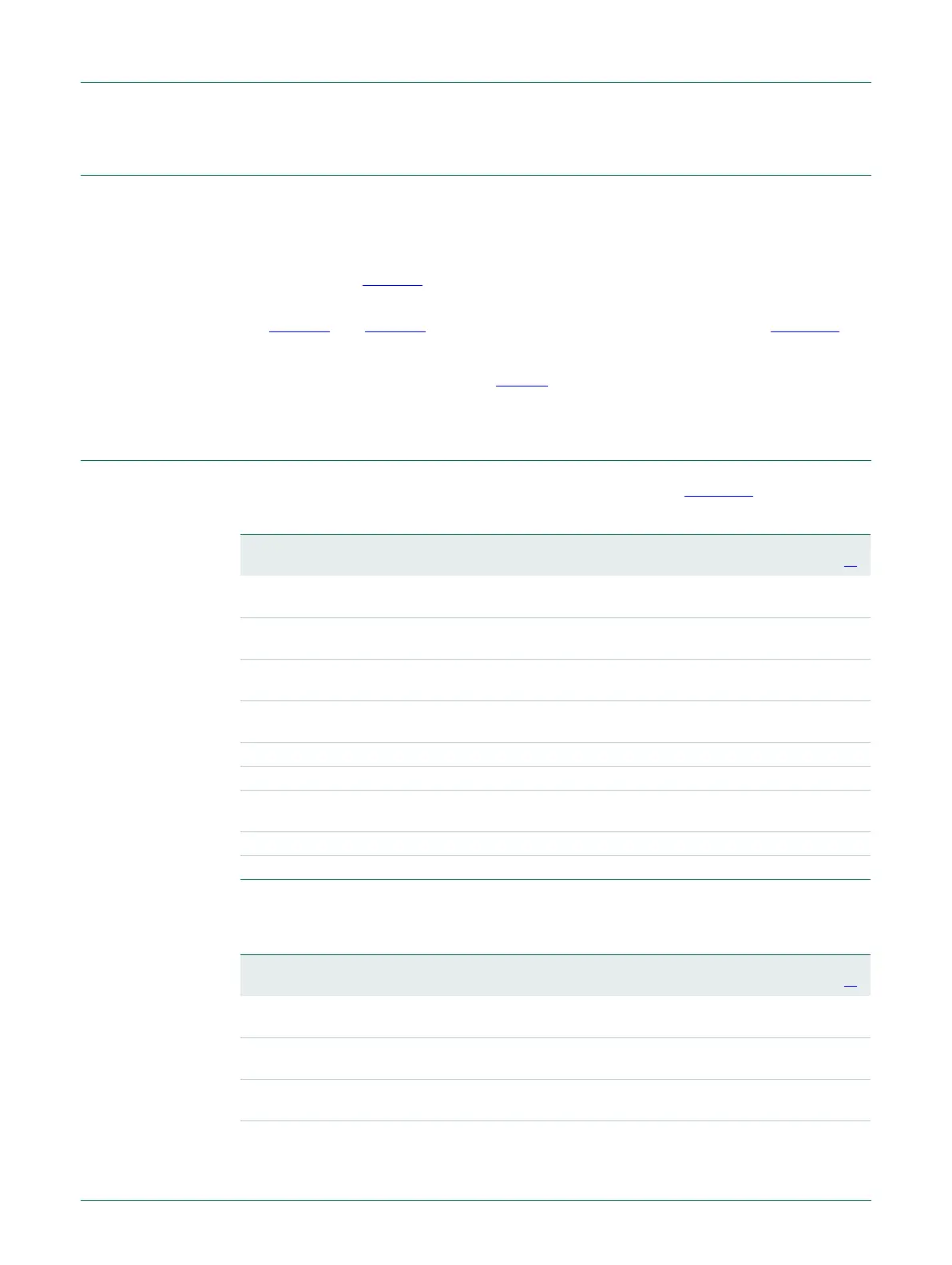

Table 242. Register overview: SSP1 (base address 0x4005 8000)

Name Access Address

offset

Description Reset

value

[1]

SSP1CR0 R/W 0x000 Control Register 0. Selects the serial clock rate,

bus type, and data size.

0

SSP1CR1 R/W 0x004 Control Register 1. Selects master/slave and

other modes.

0

SSP1DR R/W 0x008 Data Register. Writes fill the transmit FIFO, and

reads empty the receive FIFO.

0

SSP1SR RO 0x00C Status Register. 0x0000

0003

Loading...

Loading...