UM10375 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

User manual Rev. 3 — 14 June 2011 157 of 368

NXP Semiconductors

UM10375

Chapter 10: LPC13xx USB device controller

The device status change is cleared by issuing the Get device status command. All other

endpoint interrupts are cleared by issuing select endpoint/clear interrupt command.

10.11.5 Read Current Frame Number (Command: 0xF5, Data: read 1 or 2

bytes)

Returns the frame number of the last successfully received SOF. The frame number is

eleven bits wide. The frame number returns least significant byte first. In case the user is

only interested in the lower 8 bits of the frame number, only the first byte needs to be read.

• In case no SOF was received by the device at the beginning of a frame, the frame

number returned is that of the last successfully received SOF.

• In case the SOF frame number contained a CRC error, the frame number returned will

be the corrupted frame number as received by the device.

10.11.6 Read Chip ID (Command: 0xFD, Data: read 2 bytes)

The Chip ID is 16-bit wide. It returns the value the chip ID (LSB first).

10.11.7 Set Device Status (Command: 0xFE, Data: write 1 byte)

The Set Device Status command sets bits in the Device Status Register.

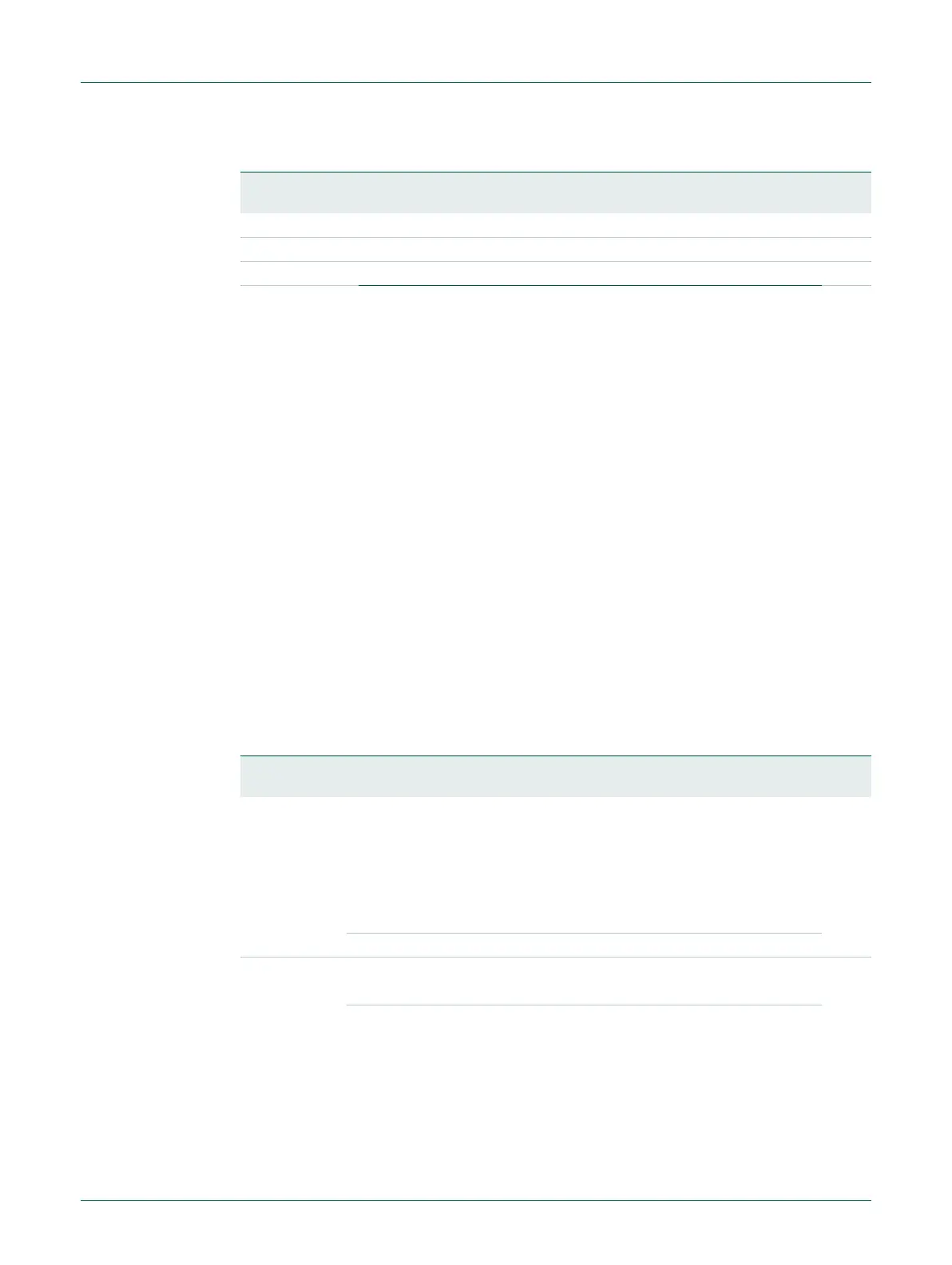

Table 180. Read interrupt Status byte 2 command description

Bit Symbol Value Description Reset

value

1:0 - reserved -

2 D_ST Device Status change interrupt 0

7:3 - reserved -

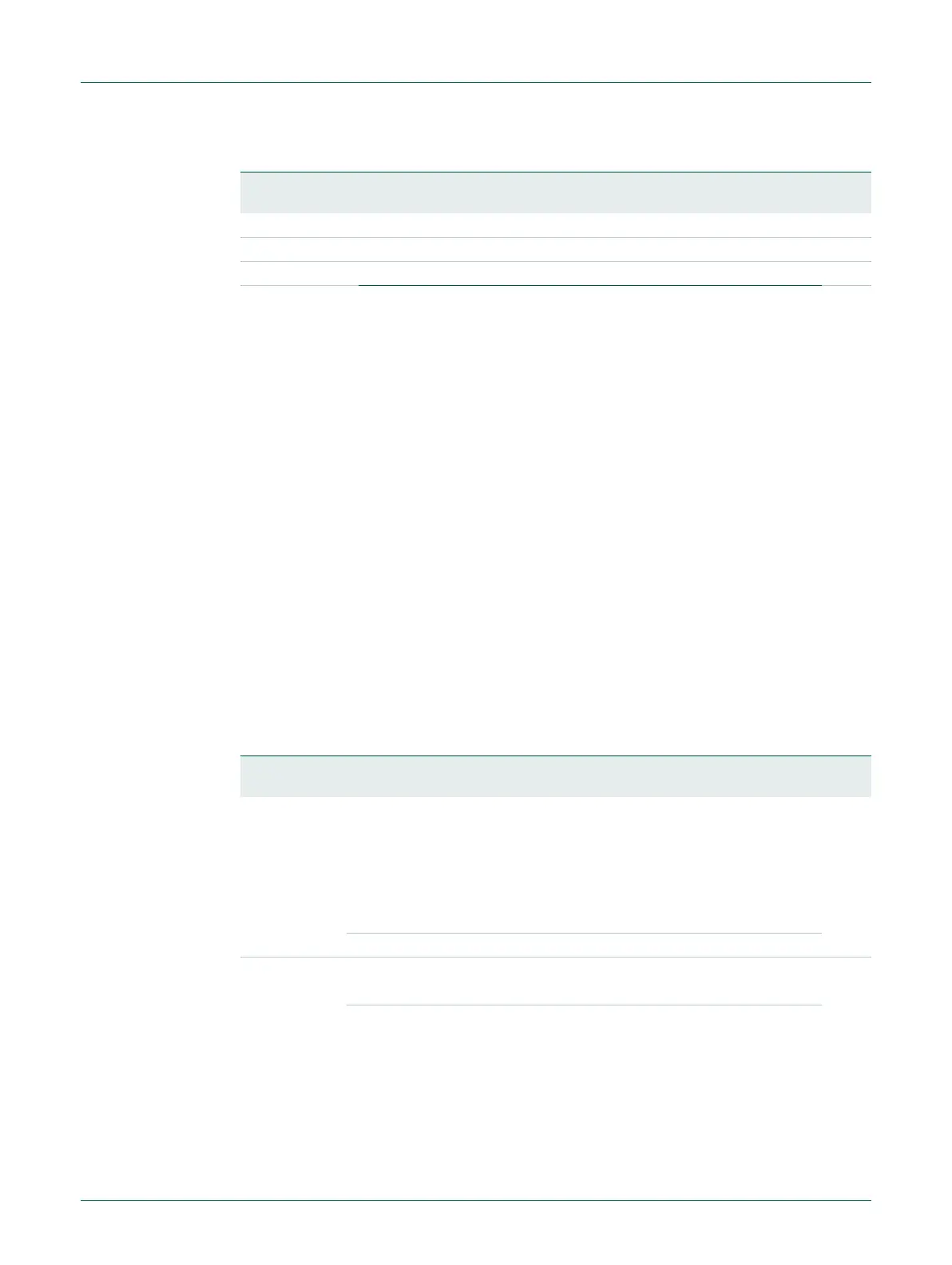

Table 181. Set Device Status command description

Bit Symbol Value Description Reset

value

0 CON The Connect bit indicates the current connect status of the

device. It controls the CONNECT output pin, used for

SoftConnect. Reading the connect bit returns the current connect

status. This bit is cleared by hardware when the V

BUS

status input

is LOW for more than 3 ms. The 3 ms delay filters out temporary

dips in the V

BUS

voltage.

0

0 Writing a 0 will make the CONNECT pin go HIGH.

1 Writing a 1 will make the CONNECT pin go LOW.

1 CON_CH Connect Change. 0

0 This bit is cleared when read.

1 This bit is set when the device’s pull-up resistor is disconnected

because V

BUS

disappeared. The DEV_STAT interrupt is

generated when this bit is 1.

Loading...

Loading...