UM10375 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

User manual Rev. 3 — 14 June 2011 143 of 368

NXP Semiconductors

UM10375

Chapter 10: LPC13xx USB device controller

[1] Reset value reflects the data stored in used bits only. It does not include reserved bits content.

[2] Reading WO register will return an invalid value.

10.10.1 Device interrupt registers

10.10.1.1 USB Device Interrupt Status register (USBDevIntSt - 0x4002 0000)

The USBDevIntSt register holds the status of each interrupt whether it is enabled or not. A

0 indicates no interrupt and 1 indicates the presence of the interrupt. USBDevIntSt is a

read only register.

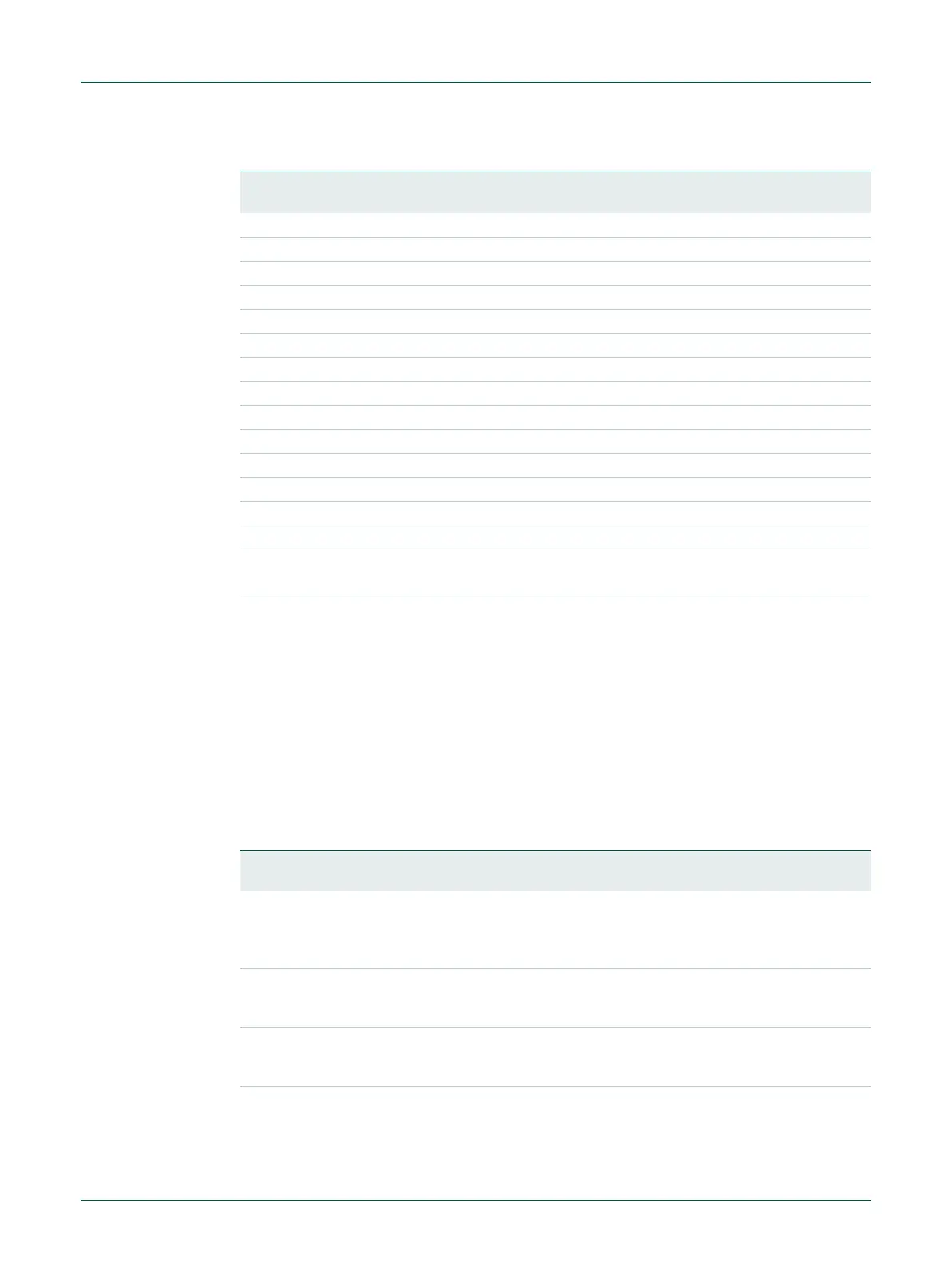

Table 162. Register overview: USB device (base address 0x4002 0000)

Name Access Address

offset

Description Reset value

Device interrupt registers

USBDevIntSt RO 0x00 USB Device Interrupt Status 0x0000 0010

USBDevIntEn R/W 0x04 USB Device Interrupt Enable 0x0000 0000

USBDevIntClr WO 0x08 USB Device Interrupt Clear 0x0000 0000

USBDevIntSet WO 0x0C USB Device Interrupt Set 0x0000 0000

SIE command registers

USBCmdCode WO 0x10 USB Command Code 0x0000 0000

USBCmdData RO 0x14 USB Command Data 0x0000 0000

USB data transfer registers

USBRxData RO 0x18 USB Receive Data 0x0000 0000

USBTxData WO 0x1C USB Transmit Data 0x0000 0000

USBRxPLen RO 0x20 USB Receive Packet Length 0x0000 0000

USBTxPLen WO 0x24 USB Transmit Packet Length 0x0000 0000

USBCtrl R/W 0x28 USB Control 0x0000 0000

Miscellaneous registers

USBDevFIQSel WO 0x2C USB Device FIQ select 0x00

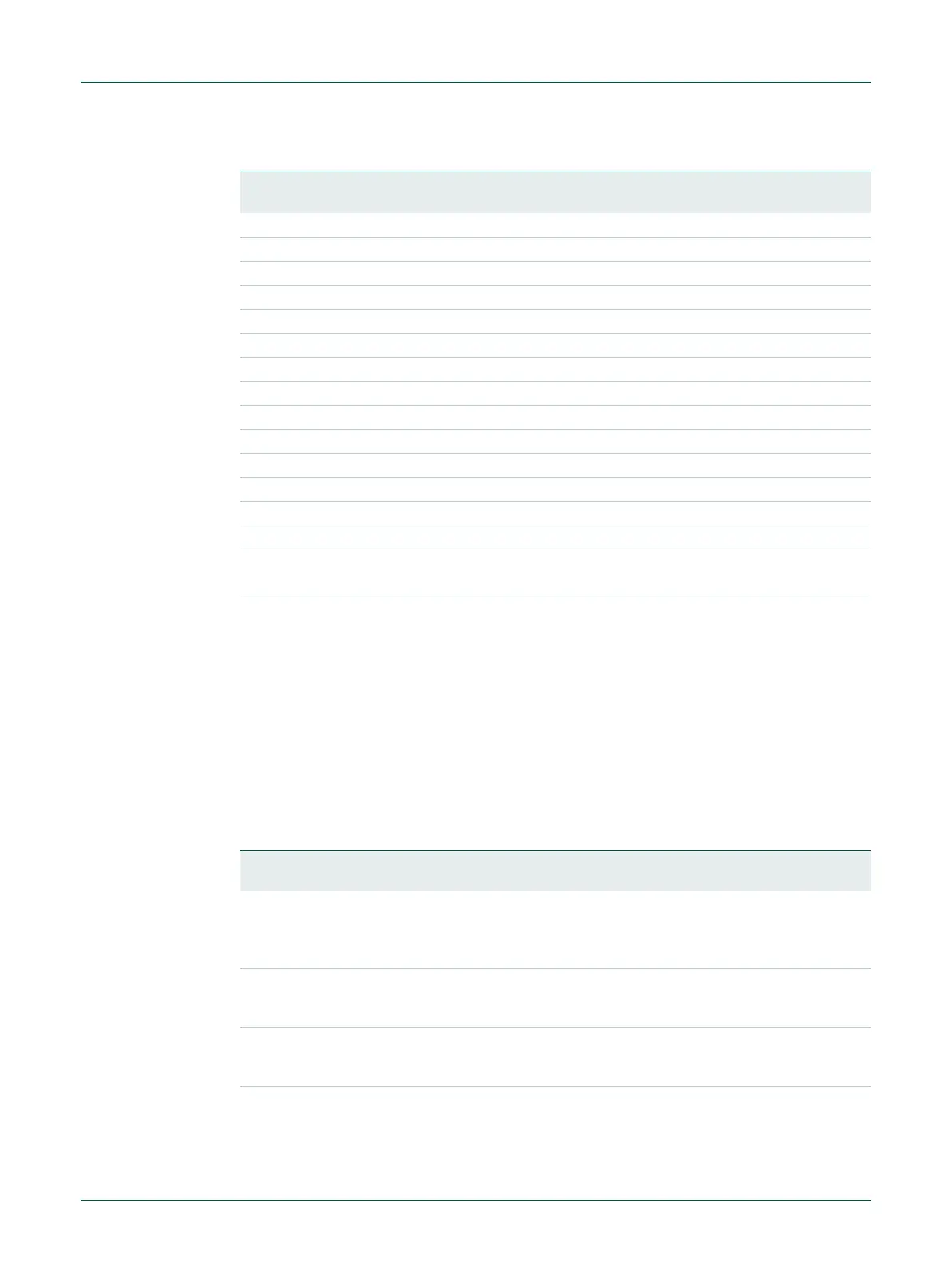

Table 163. USB Device Interrupt Status register (USBDevIntSt - address 0x4002 0000) bit

description

Bit Symbol Description Reset

value

0 FRAME The frame interrupt occurs every 1 ms. This is used in

isochronous packet transfers.

0 = no interrupt.

1 = interrupt pending.

-

1 EP0 USB core interrupt for physical endpoint 0.

0 = no interrupt.

1 = interrupt pending.

-

2 EP1 USB core interrupt for physical endpoint 1.

0 = no interrupt.

1 = interrupt pending.

-

3 EP2 USB core interrupt for physical endpoint 2.

0 = no interrupt.

1 = interrupt pending.

-

Loading...

Loading...