UM10375 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

User manual Rev. 3 — 14 June 2011 273 of 368

NXP Semiconductors

UM10375

Chapter 15: LPC13xx 16-bit timer/counters (CT16B0/1)

15.8.8 Capture Control Register (TMR16B0CCR and TMR16B1CCR)

The Capture Control Register is used to control whether the Capture Register is loaded

with the value in the Counter/timer when the capture event occurs, and whether an

interrupt is generated by the capture event. Setting both the rising and falling bits at the

same time is a valid configuration, resulting in a capture event for both edges. In the

description below, "n" represents the Timer number, 0 or 1.

15.8.9 Capture Register (CT16B0CR0 - address 0x4000 C02C and

CT16B1CR0 - address 0x4001 002C)

Each Capture register is associated with a device pin and may be loaded with the

counter/timer value when a specified event occurs on that pin. The settings in the Capture

Control Register register determine whether the capture function is enabled, and whether

a capture event happens on the rising edge of the associated pin, the falling edge, or on

both edges.

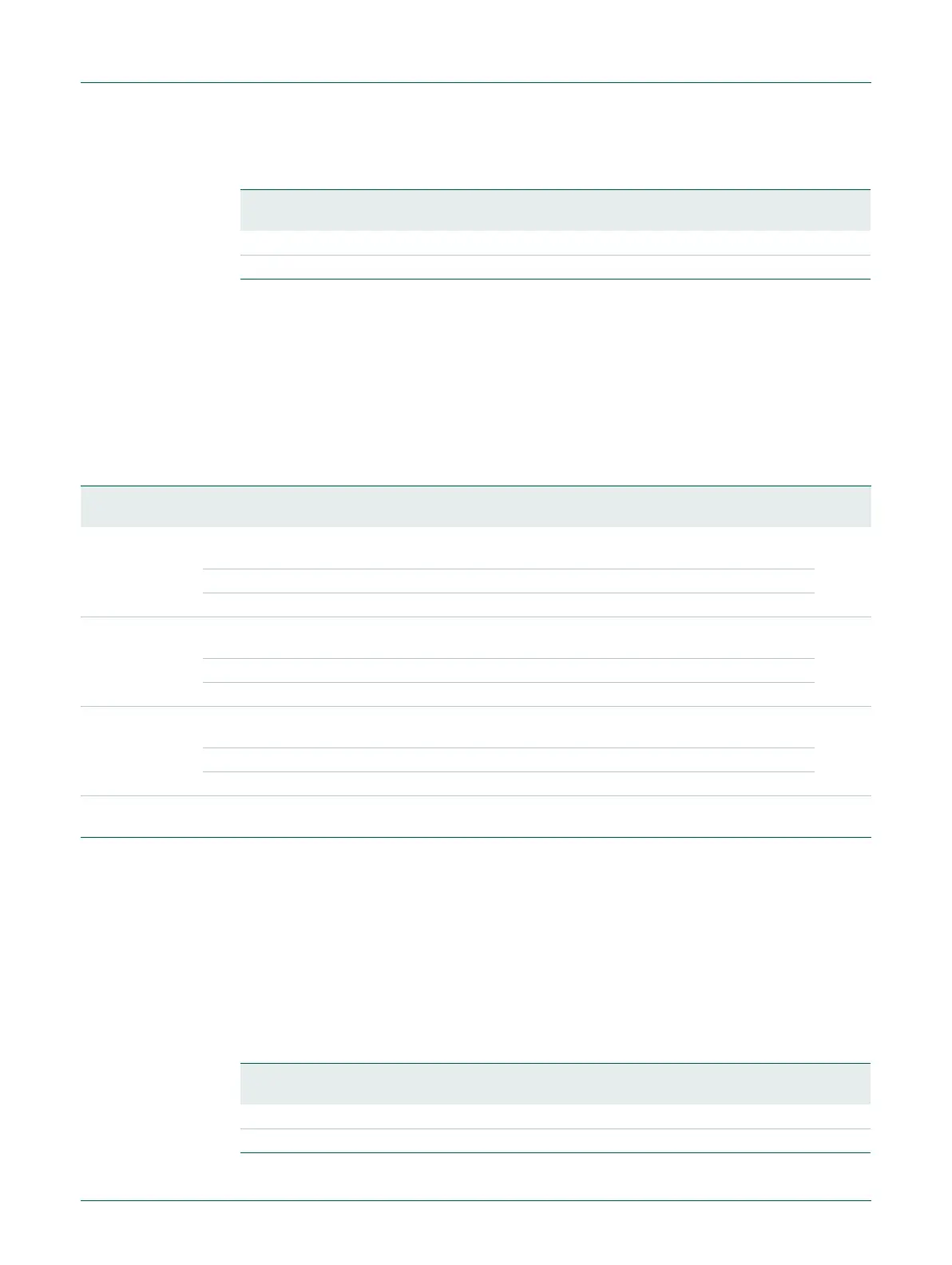

Table 261: Match registers (TMR16B0MR0 to 3, addresses 0x4000 C018 to 24 and

TMR16B1MR0 to 3, addresses 0x4001 0018 to 24) bit description

Bit Symbol Description Reset

value

15:0 MATCH Timer counter match value. 0

31:16 - Reserved. -

Table 262. Capture Control Register (TMR16B0CCR - address 0x4000 C028 and TMR16B1CCR - address

0x4001 0028) bit description

Bit Symbol Value Description Reset

value

0 CAP0RE Capture on CT16Bn_CAP0 rising edge: a sequence of 0 then 1 on CT16Bn_CAP0 will

cause CR0 to be loaded with the contents of TC.

0

1 Enabled

0 Disabled

1 CAP0FE Capture on CT16Bn_CAP0 falling edge: a sequence of 1 then 0 on CT16Bn_CAP0 will

cause CR0 to be loaded with the contents of TC.

0

1 Enabled

0 Disabled

2 CAP0I Interrupt on CT16Bn_CAP0 event: a CR0 load due to a CT16Bn_CAP0 event will

generate an interrupt.

0

1 Enabled

0 Disabled

31:3 - - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

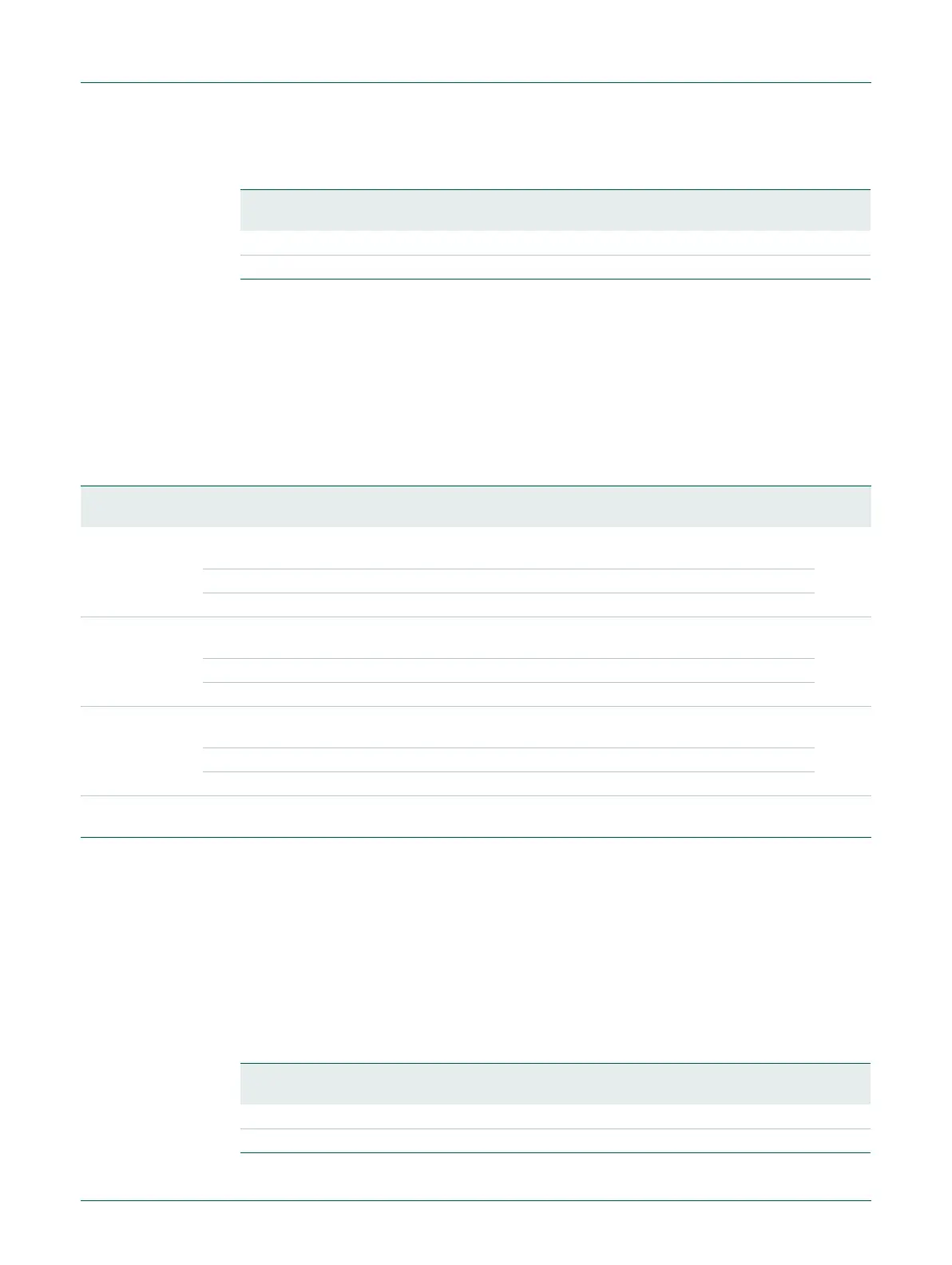

Table 263: Capture registers (TMR16B0CR0, address 0x4000 C02C and TMR16B1CR0,

address 0x4001 002C) bit description

Bit Symbol Description Reset

value

15:0 CAP Timer counter capture value. 0

31:16 - Reserved. -

Loading...

Loading...