UM10375 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

User manual Rev. 3 — 14 June 2011 36 of 368

NXP Semiconductors

UM10375

Chapter 3: LPC13xx System configuration

Every bit in the STARTAPRP1 register controls one port input and is connected to one

wake-up interrupt in the NVIC. Bit 0 in the STARTAPRP1 register corresponds to interrupt

32, bit 1 to interrupt 33, up to bit 7 corresponding to interrupt 39 (see Table 66

).

Remark: Each interrupt connected to a start logic input must be enabled in the NVIC if the

corresponding PIO pin is used to wake up the chip from Deep-sleep mode.

3.5.42 Start logic signal enable register 1

This STARTERP1 register enables or disables the start signal bits in the start logic. The bit

assignment is identical to Table 48

.

3.5.43 Start logic reset register 1

Writing a one to a bit in the STARTRSRP1CLR register resets the start logic state. The bit

assignment is identical to Table 48

. The start-up logic uses the input signals to generate a

clock edge for registering a start signal. This clock edge (falling or rising) sets the interrupt

for waking up from Deep-sleep mode. Therefore, the start-up logic states must be cleared

before being used.

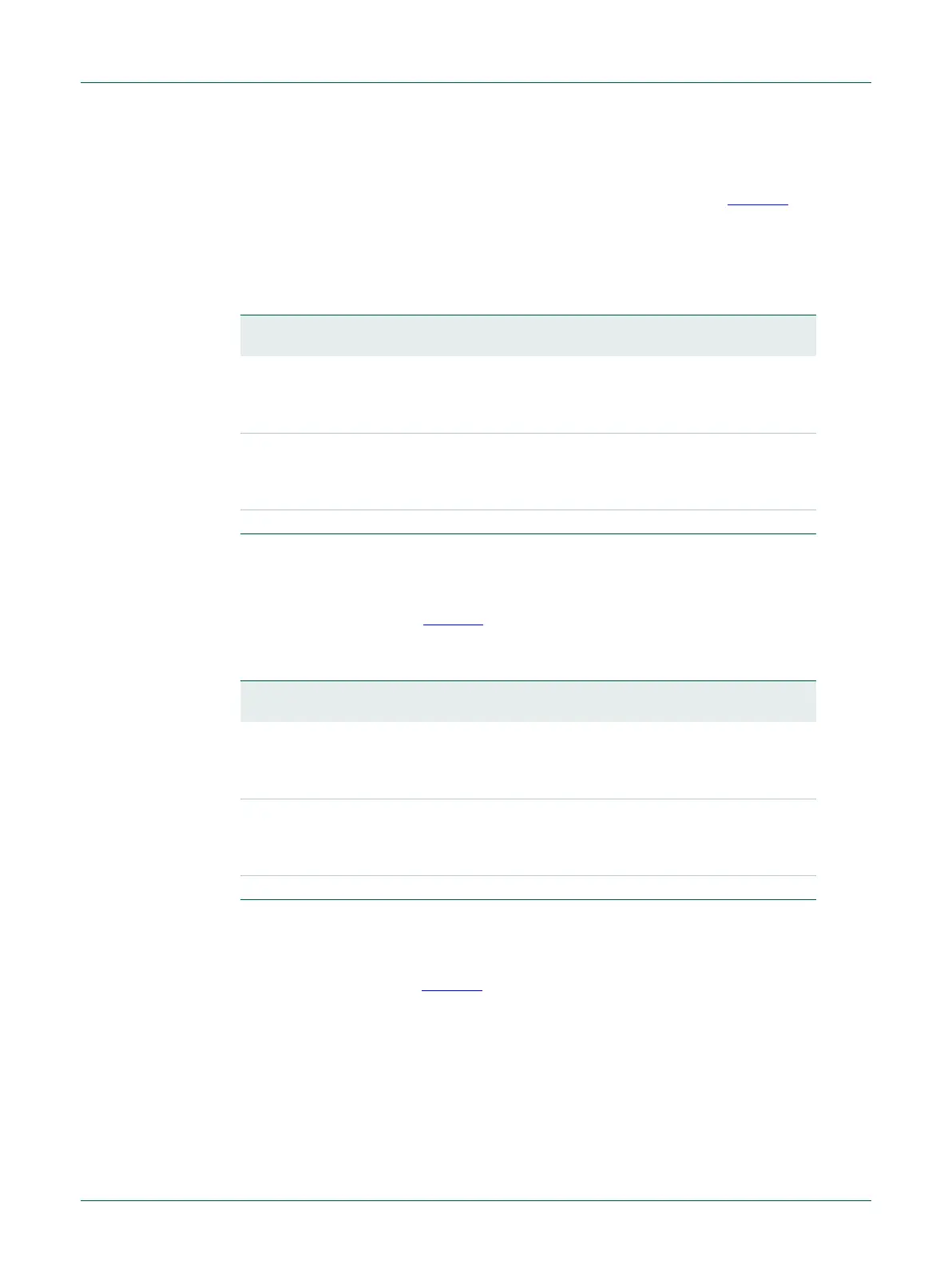

Table 48. Start logic edge control register 1 (STARTAPRP1, address 0x4004 8210) bit

description

Bit Symbol Description Reset

value

3:0 APRPIO2_n Edge select for start logic input PIO2_n (bit 0 = PIO2_8,

..., bit 3 = PIO2_11).

0 = Falling edge.

1 = Rising edge.

0

7:4 APRPIO3_n Edge select for start logic input PIO3_n (bit 4 = PIO3_0,

..., bit 7 = PIO3_3).

0 = Falling edge.

1 = Rising edge.

0

31:8 - Reserved 0

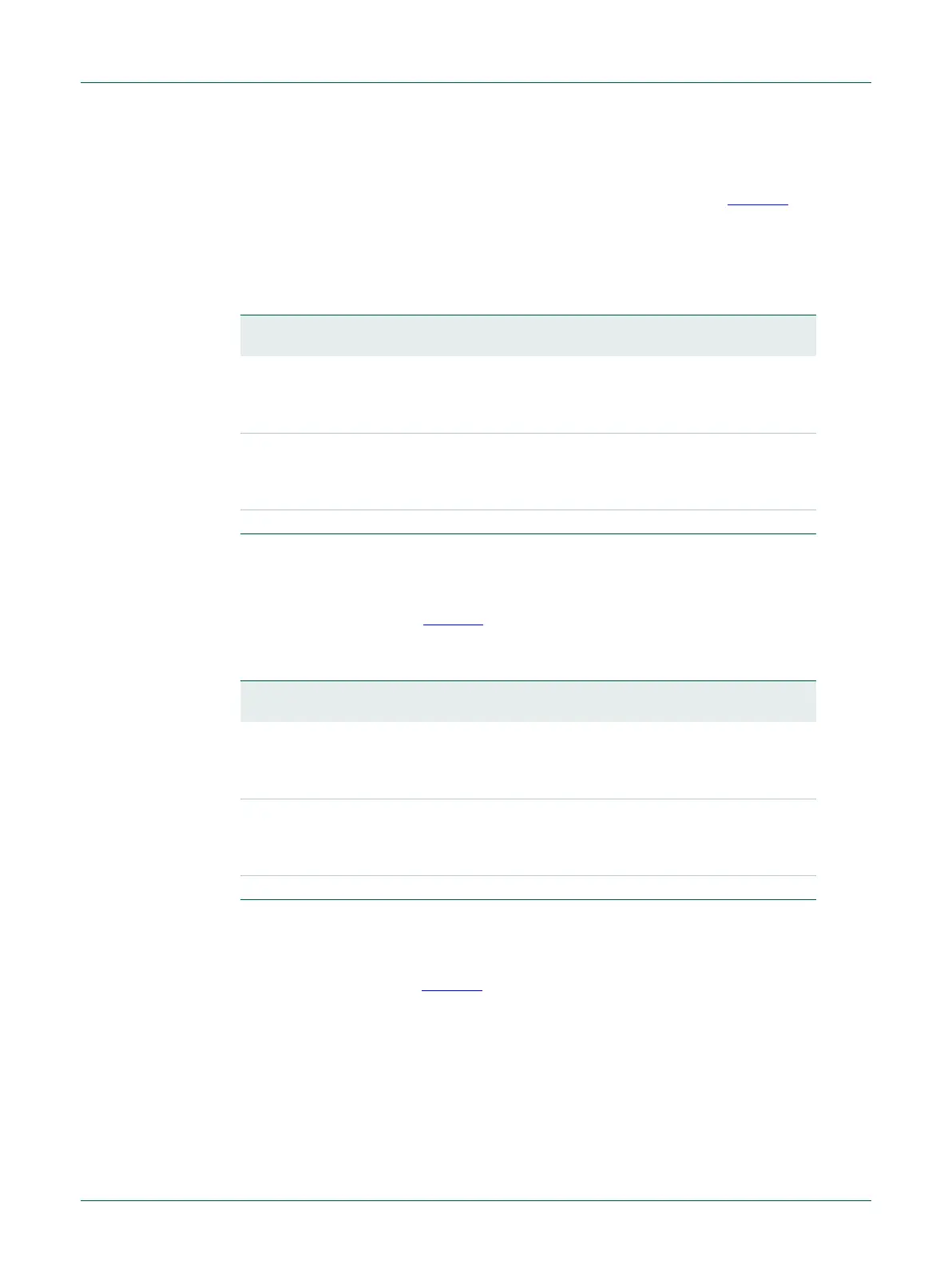

Table 49. Start logic signal enable register 1 (STARTERP1, address 0x4004 8214) bit

description

Bit Symbol Description Reset

value

3:0 ERPIO2_n Enable start signal for start logic input PIO2_n (bit 0 =

PIO2_8, ..., bit 3 = PIO2_11).

0 = Disabled.

1 = Enabled.

0

7:4 ERPIO3_n Enable start signal for start logic input PIO3_n (bit 4 =

PIO3_0, ..., bit 7 = PIO3_3).

0 = Disabled.

1 = Enabled.

0

31:8 - Reserved 0

Loading...

Loading...