RM0033 Rev 9 1023/1381

RM0033 USB on-the-go full-speed (OTG_FS)

1097

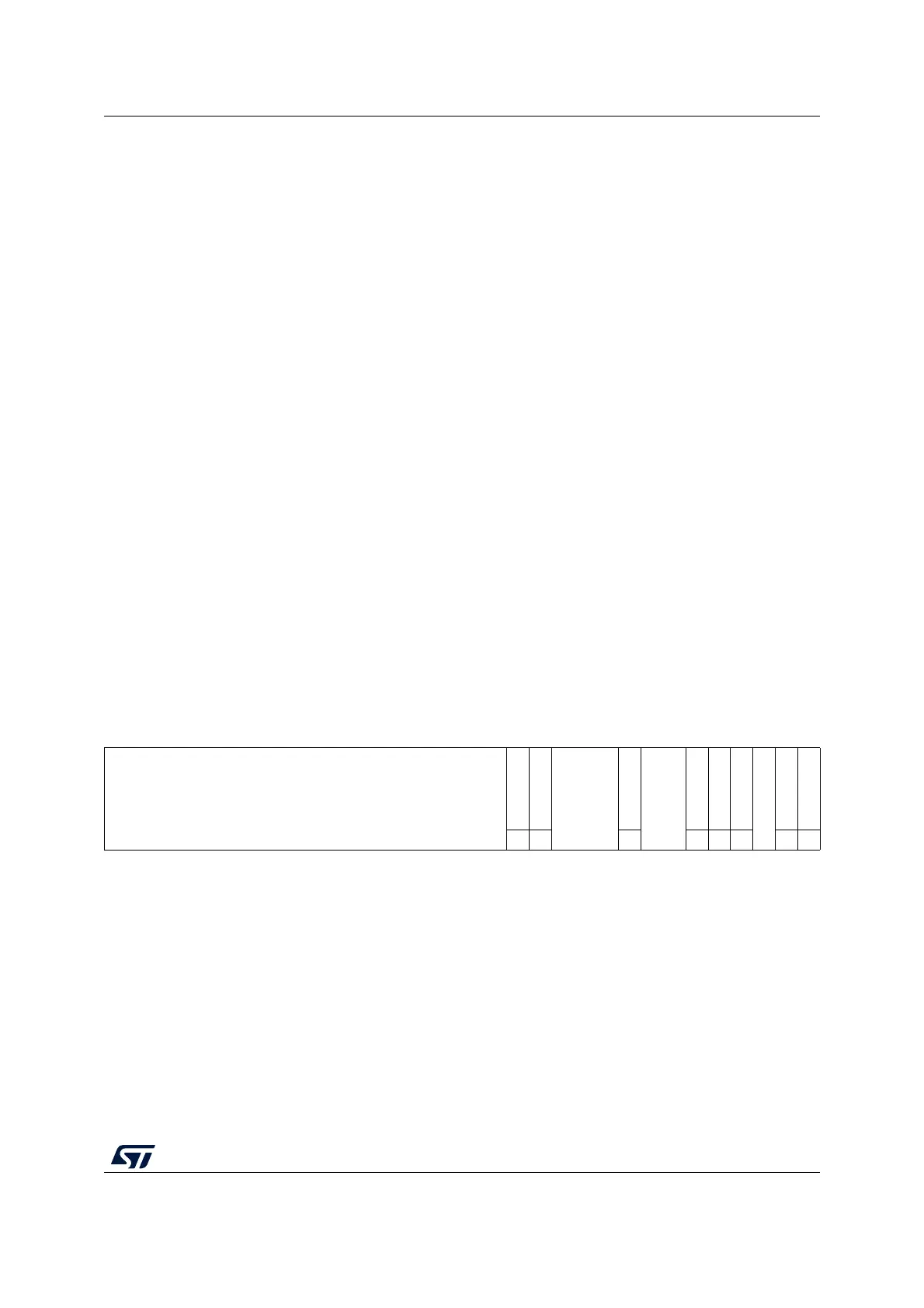

OTG_FS device OUT endpoint common interrupt mask register

(OTG_FS_DOEPMSK)

Address offset: 0x814

Reset value: 0x0000 0000

This register works with each of the OTG_FS_DOEPINTx registers for all endpoints to

generate an interrupt per OUT endpoint. The OUT endpoint interrupt for a specific status in

the OTG_FS_DOEPINTx register can be masked by writing into the corresponding bit in this

register. Status bits are masked by default.

Bit 5 INEPNMM: IN token received with EP mismatch mask

0: Masked interrupt

1: Unmasked interrupt

Bit 4 ITTXFEMSK: IN token received when TxFIFO empty mask

0: Masked interrupt

1: Unmasked interrupt

Bit 3 TOM: Timeout condition mask (Non-isochronous endpoints)

0: Masked interrupt

1: Unmasked interrupt

Bit 2 Reserved, must be kept at reset value.

Bit 1 EPDM: Endpoint disabled interrupt mask

0: Masked interrupt

1: Unmasked interrupt

Bit 0 XFRCM: Transfer completed interrupt mask

0: Masked interrupt

1: Unmasked interrupt

313029282726252423222120191817161514131211109876543210

Reserved

NAK

BERRM

Reserved

OUTPKTERRM

Reserved

STSPHSRXM

OTEPDM

STUPM

Reserved

EPDM

XFRCM

rw rw rw rw rw rw rw rw

Bits 31:14 Reserved, must be kept at reset value.

Bit 13 NAKMSK: NAK interrupt mask

0: Masked interrupt

1: Unmasked interrupt

Bit 12 BERRM: Babble error interrupt mask

0: Masked interrupt

1: Unmasked interrupt

Bits 11:9 Reserved, must be kept at reset value.

Bit 8 OUTPKTERRM: Out packet error mask

0: Masked interrupt

1: Unmasked interrupt

Loading...

Loading...