RM0033 Rev 9 49/1381

RM0033 Memory and bus architecture

60

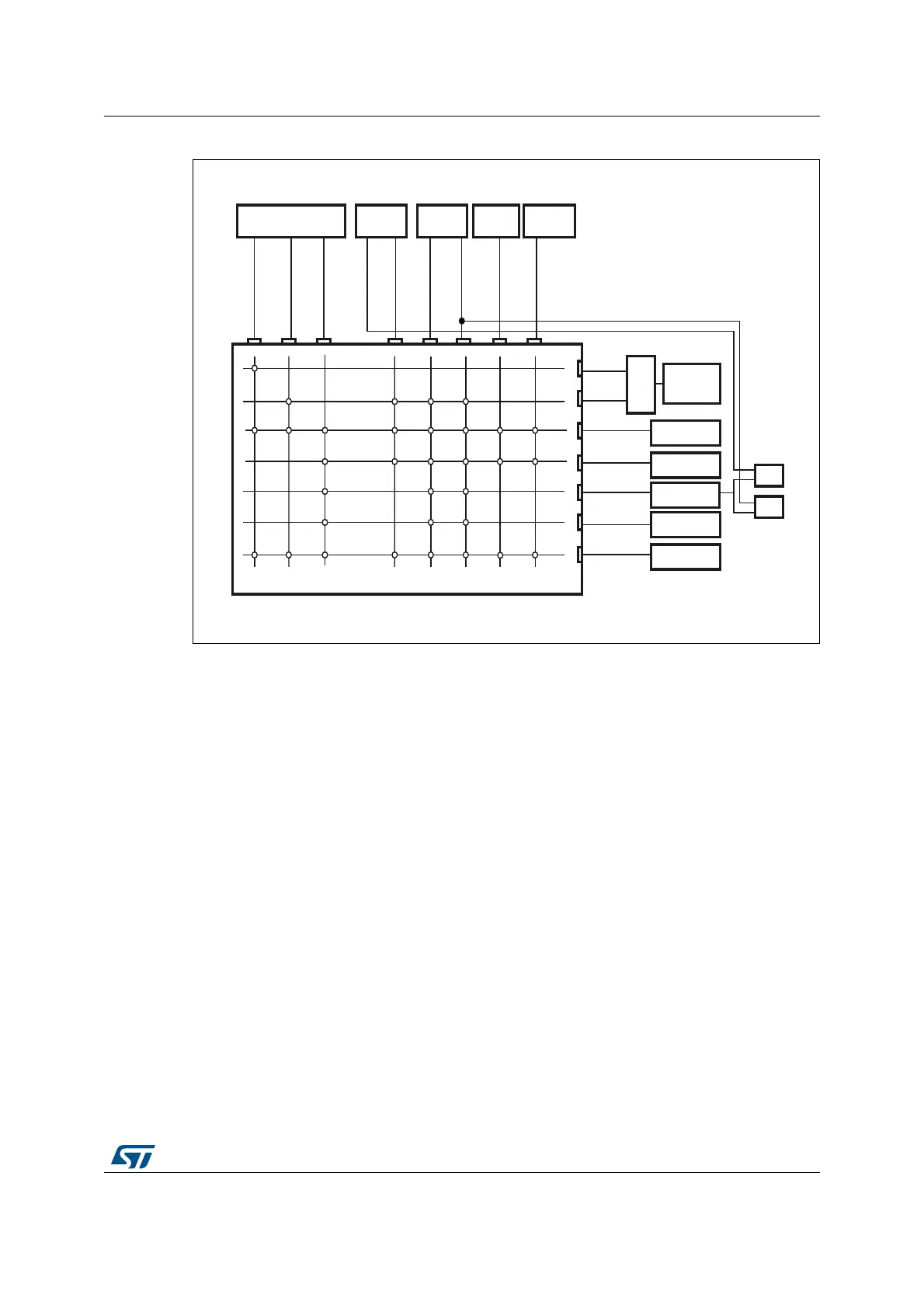

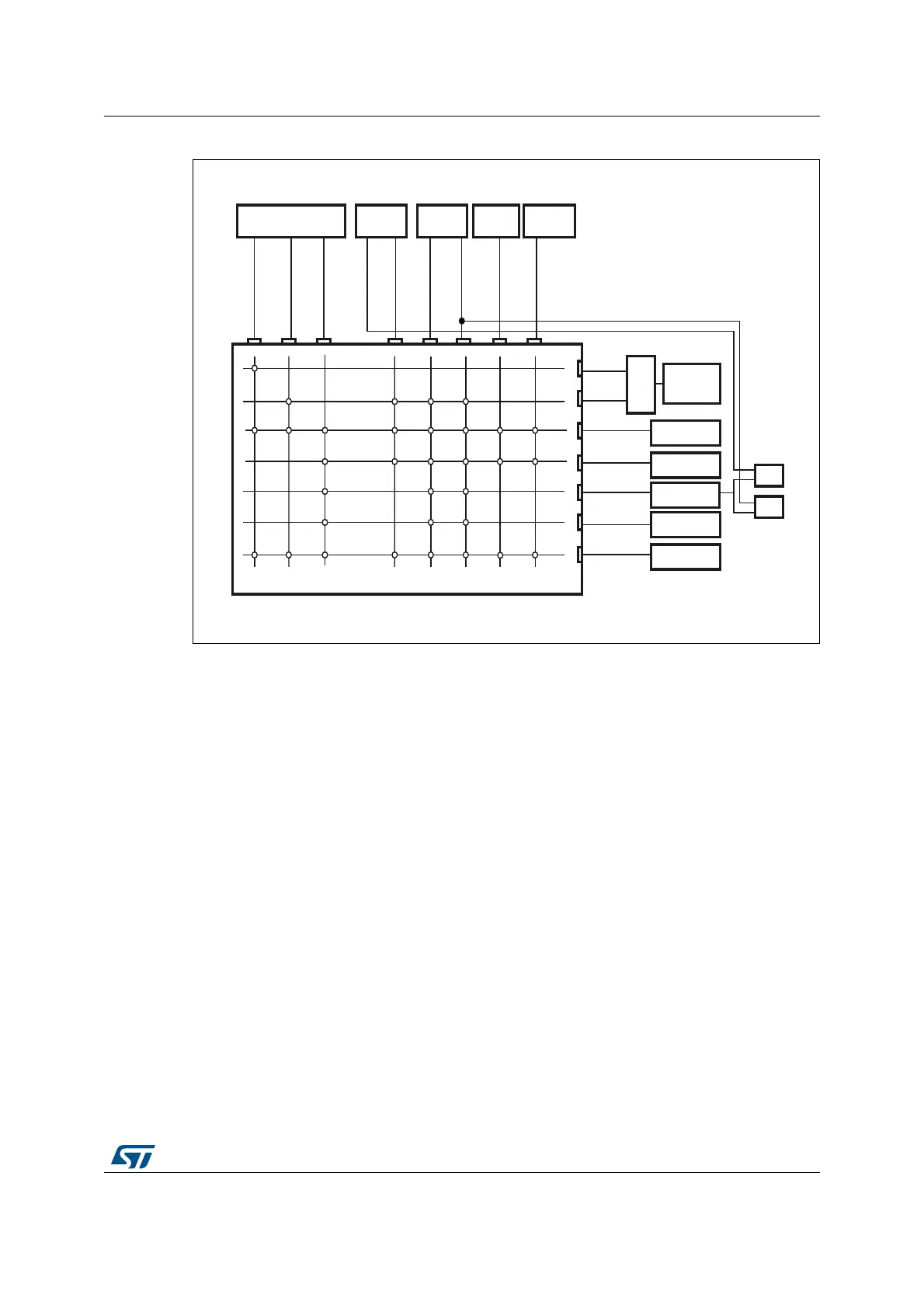

Figure 1. System architecture

2.1.1 S0: I-bus

This bus connects the Instruction bus of the Cortex

®

-M3 core to the BusMatrix. This bus is

used by the core to fetch instructions. The target of this bus is a memory containing code

(internal Flash memory/SRAM or external memories through the FSMC).

2.1.2 S1: D-bus

This bus connects the databus of the Cortex

®

-M3 to the BusMatrix. This bus is used by the

core for literal load and debug access. The target of this bus is a memory containing code or

data (internal Flash memory /SRAM or external memories through the FSMC).

2.1.3 S2: S-bus

This bus connects the system bus of the Cortex

®

-M3 core to a BusMatrix. This bus is used

to access data located in a peripheral or in SRAM. Instructions may also be fetch on this bus

(less efficient than ICode). The targets of this bus are the 112 KB & 16 KB internal SRAMs,

the AHB1 peripherals including the APB peripherals, the AHB2 peripherals and the external

memories through the FSMC.

2.1.4 S3, S4: DMA memory bus

This bus connects the DMA memory bus master interface to the BusMatrix. It is used by the

DMA to perform transfer to/from memories. The targets of this bus are data memories:

internal SRAM and external memories through the FSMC.

ARM

Cortex-M3

GP

DMA1

GP

DMA2

MAC

Ethernet

USB OTG

HS

Bus matrix-S

S0 S1 S2 S3 S4 S5 S6 S7

ICODE

DCODE

ART

ACCEL.

Flash

memory

SRAM

112 Kbyte

SRAM

16 Kbyte

AHB

periph 1

AHB

periph 2

FSMC

Static MemCtl

M0

M1

M2

M3

M4

M5

M6

I-bus

D-bus

S-bus

DMA_P1

DMA_MEM1

DMA_MEM2

DMA_P2

ETHERNET_M

USB_HS_M

ai15963b

APB1

APB2

Loading...

Loading...