Window watchdog (WWDG) RM0033

504/1381 RM0033 Rev 9

As an example, let us assume APB1 frequency is equal to 24 MHz, WDGTB[1:0] is set to 3

and T[5:0] is set to 63:

Refer to Table 71 for the minimum and maximum values of the t

WWDG

.

18.5 Debug mode

When the microcontroller enters debug mode (Cortex

®

-M3 core halted), the WWDG counter

either continues to work normally or stops, depending on DBG_WWDG_STOP

configuration bit in DBG module. For more details, refer to Section 32.16.2: Debug support

for timers, watchdog, bxCAN and I

2

C.

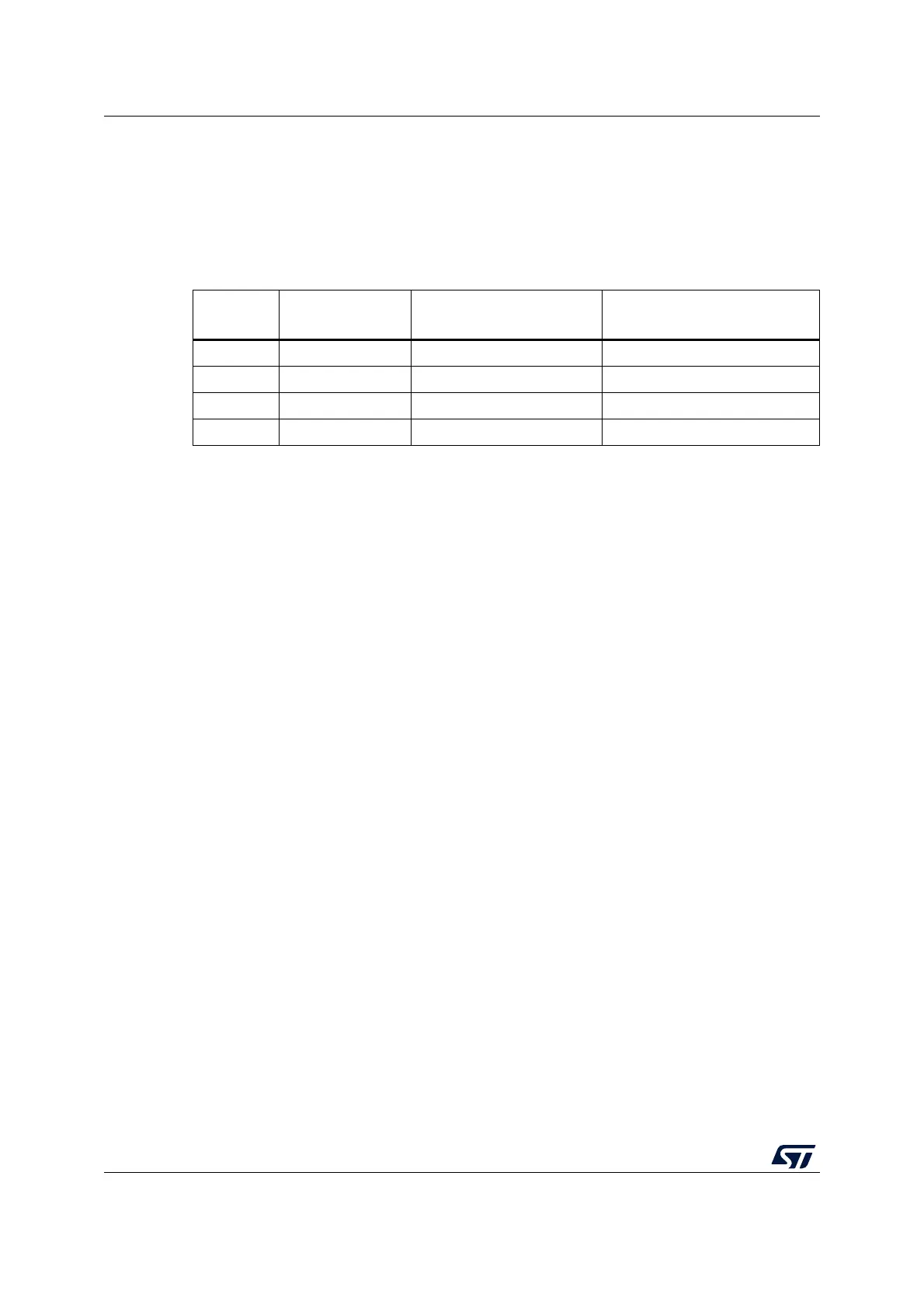

Table 71. Minimum and maximum timeout values at 30 MHz (f

PCLK1

)

Prescaler WDGTB

Min timeout (µs)

T[5:0] = 0x00

Max timeout (ms)

T[5:0] = 0x3F

1 0 136.53 8.74

2 1 273.07 17.48

4 2 546.13 34.95

8 3 1092.27 69.91

t

WWDG

1 24000⁄ 4096× 2

3

× 63 1+()× 21.85ms==

Loading...

Loading...