Ethernet (ETH): media access control (MAC) with DMA controller RM0033

894/1381 RM0033 Rev 9

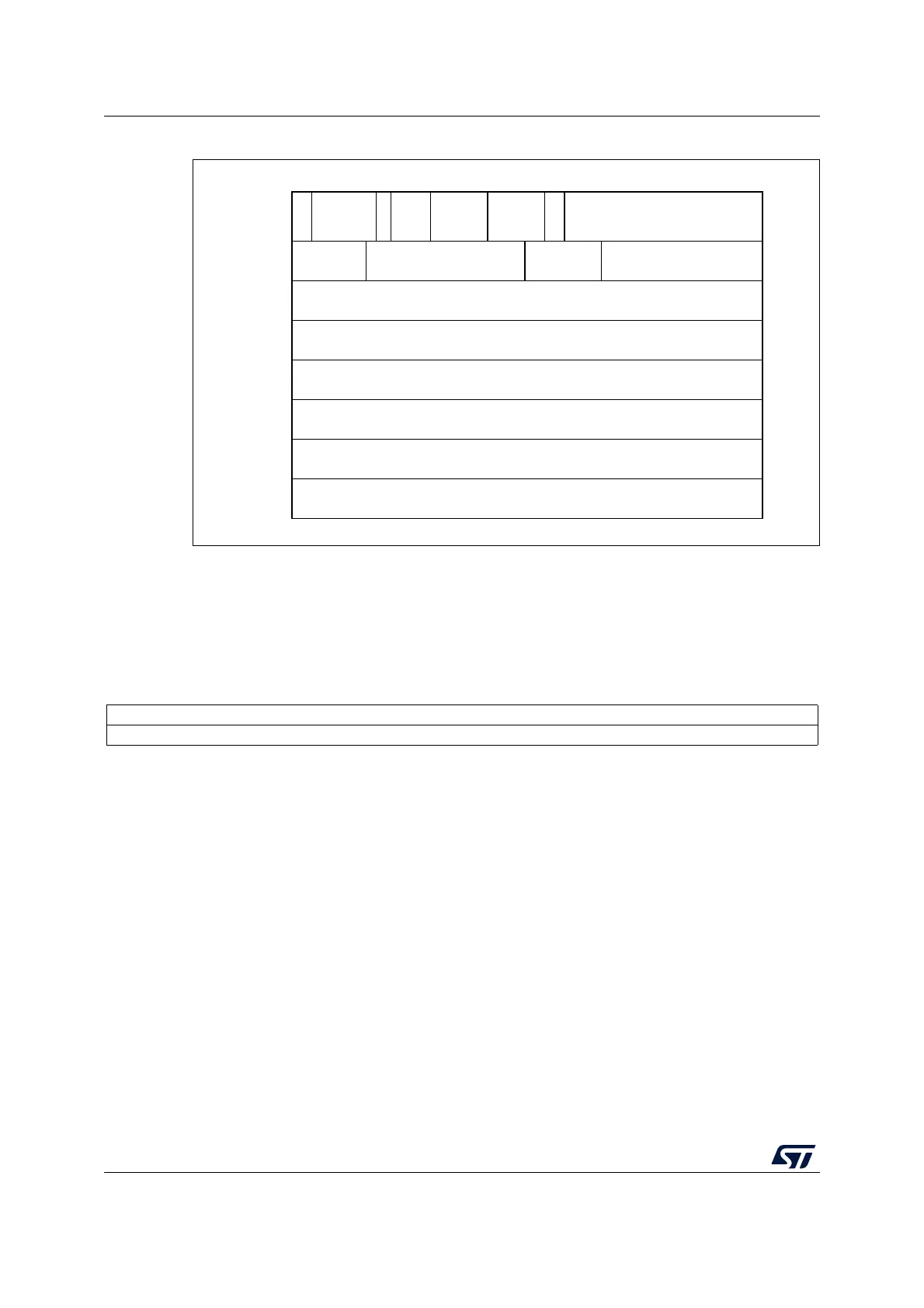

Figure 343. Enhanced transmit descriptor

• TDES4: Transmit descriptor Word4

Reserved

• TDES5: Transmit descriptor Word5

Reserved

• TDES6: Transmit descriptor Word6

TDES 3

O

W

N

Ctrl

[30:26]

Res.

24

Ctrl

[23:20]

Reserved

[19:18]

Status [16:0]

Reserved

[31:29]

Buffer 2 byte count

[28:16]

Reserved

[15:13]

Buffer 1 byte count

[12:0]

Buffer 1 address [31:0]

Buffer 2 address [31:0] or Next descriptor address [31:0]

TDES 0

TDES 1

TDES 2

31 0

ai17105b

T

T

S

E

T

T

S

S

TDES 7

TDES 4

TDES 5

TDES 6

Reserved

Reserved

Time stamp low [31:0]

Time stamp high [31:0]

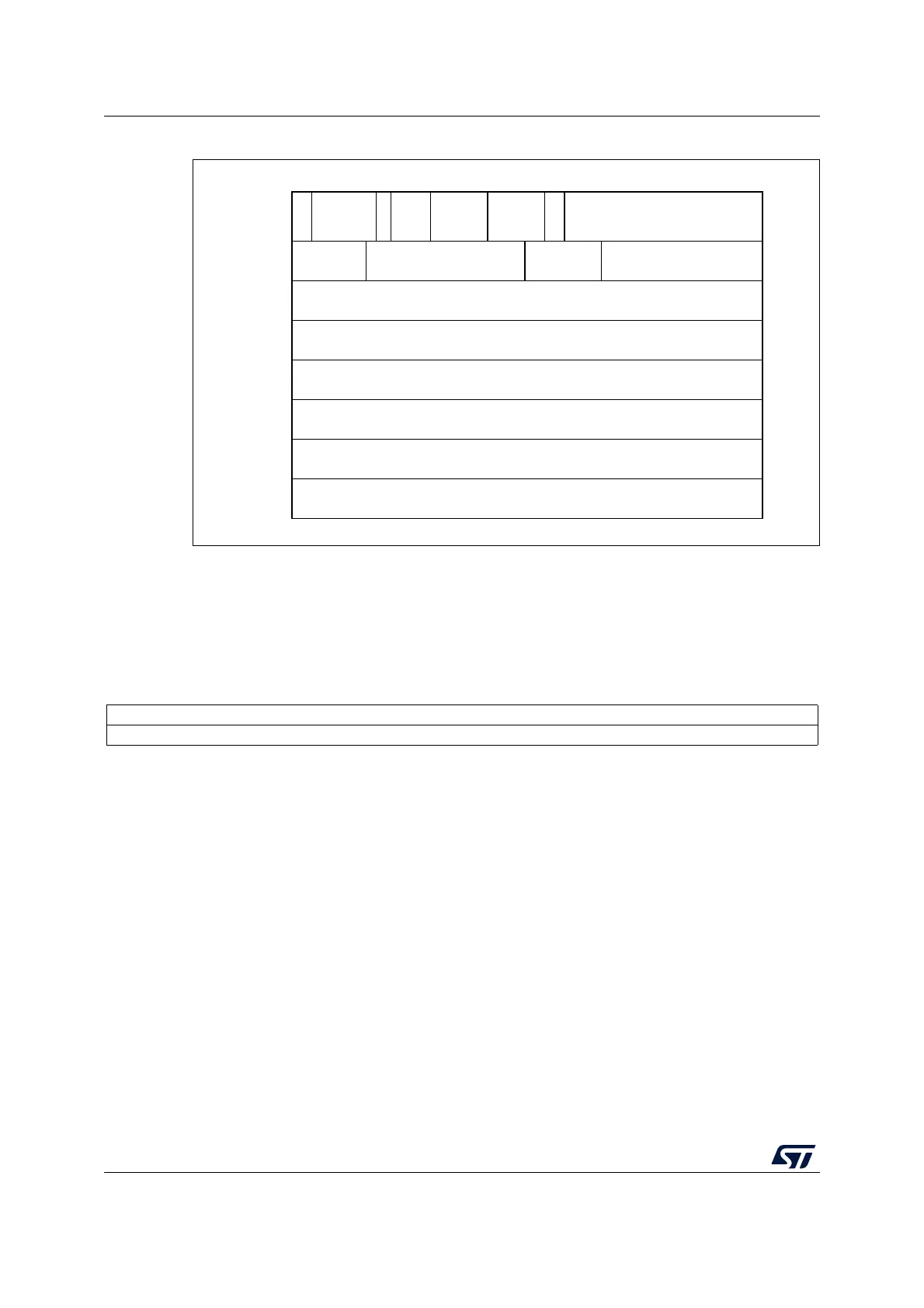

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TTSL

rw

Bits 31:0 TTSL: Transmit frame time stamp low

This field is updated by DMA with the 32 least significant bits of the time stamp captured

for the corresponding transmit frame. This field has the time stamp only if the Last segment

control bit (LS) in the descriptor is set.

Loading...

Loading...