System configuration controller (SYSCFG) RM0033

162/1381 RM0033 Rev 9

7.2.6 SYSCFG external interrupt configuration register 4

(SYSCFG_EXTICR4)

Address offset: 0x14

Reset value: 0x0000

7.2.7 Compensation cell control register (SYSCFG_CMPCR)

Address offset: 0x20

Reset value: 0x0000 0000

Bits 31:16 Reserved

Bits 15:0 EXTIx[3:0]: EXTI x configuration (x = 8 to 11)

These bits are written by software to select the source input for the EXTIx external interrupt.

0000: PA[x] pin

0001: PB[x] pin

0010: PC[x] pin

0011: PD[x] pin

0100: PE[x] pin

0101: PF[x] pin

0110: PG[x] pin

0111: PH[x] pin

1000: PI[x] pin

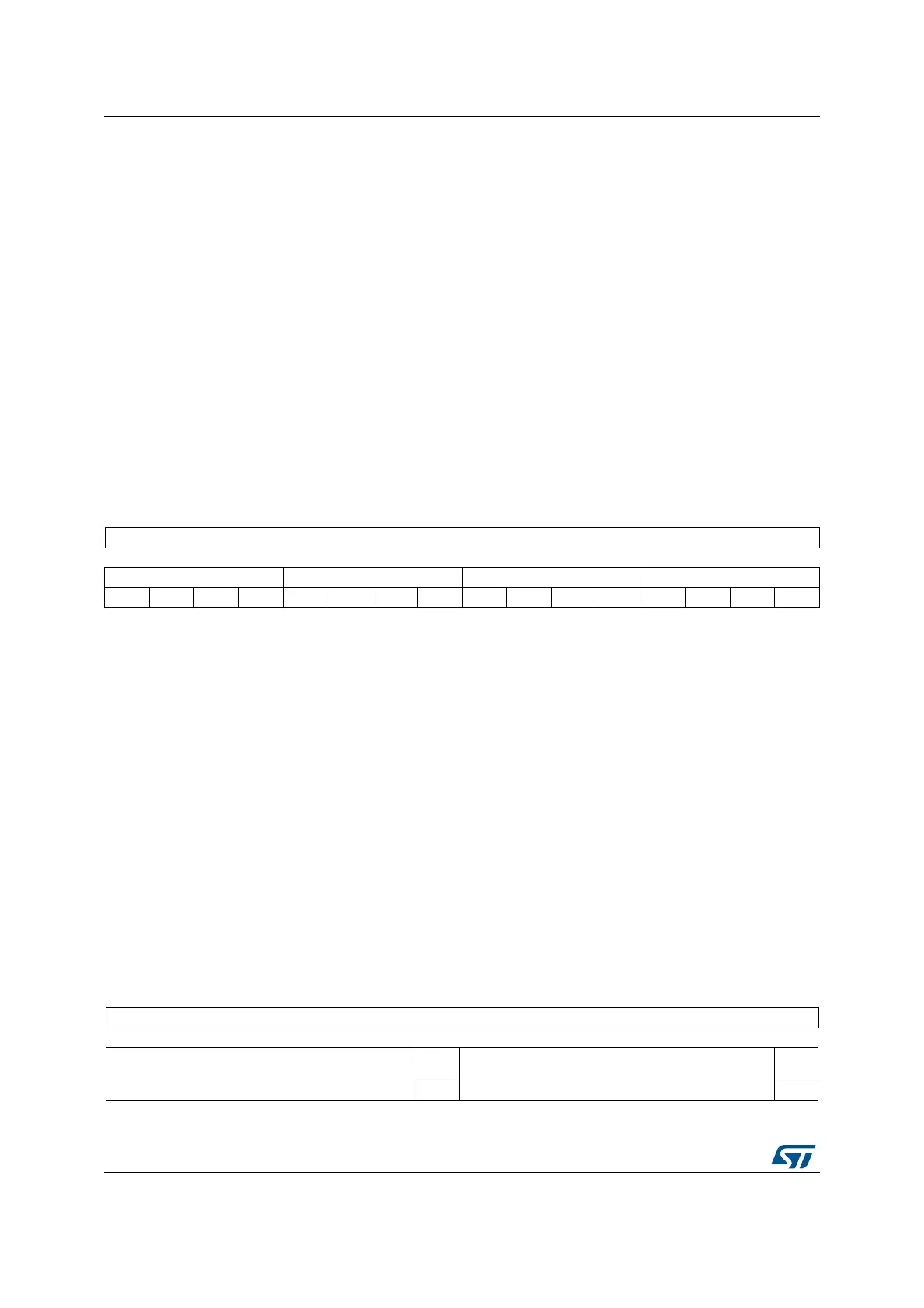

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

1514131211109876543210

EXTI15[3:0] EXTI14[3:0] EXTI13[3:0] EXTI12[3:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:16 Reserved

Bits 15:0 EXTIx[3:0]: EXTI x configuration (x = 12 to 15)

These bits are written by software to select the source input for the EXTIx external interrupt.

0000: PA[x] pin

0001: PB[x] pin

0010: PC[x] pin

0011: PD[x] pin

0100: PE[x] pin

0101: PF[x] pin

0110: PG[x] pin

0111: PH[x] pin

Note: PI[15:12] are not used.

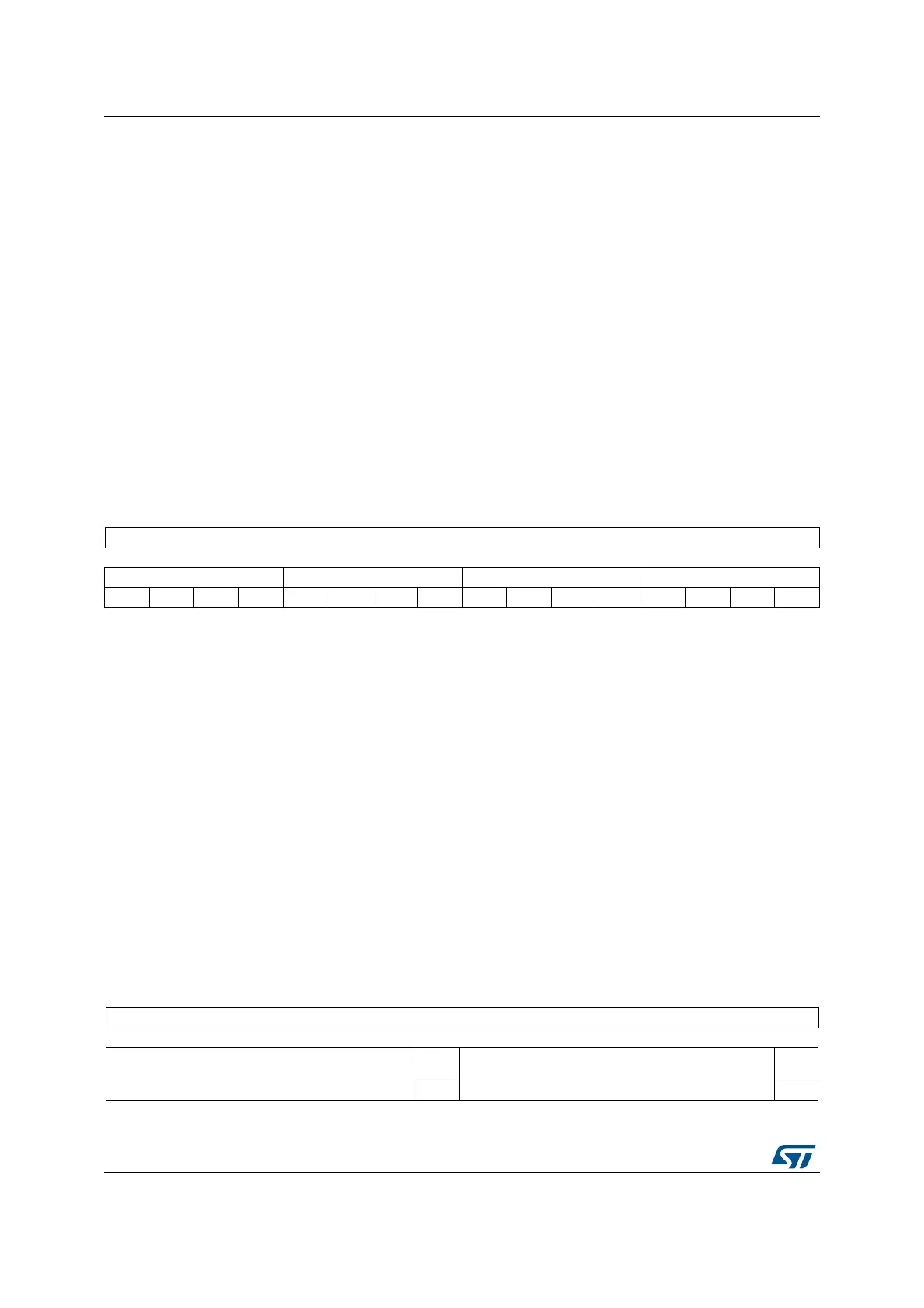

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

READY

Reserved

CMP_

PD

r rw

Loading...

Loading...