RM0033 Rev 9 293/1381

RM0033 Digital camera interface (DCMI)

302

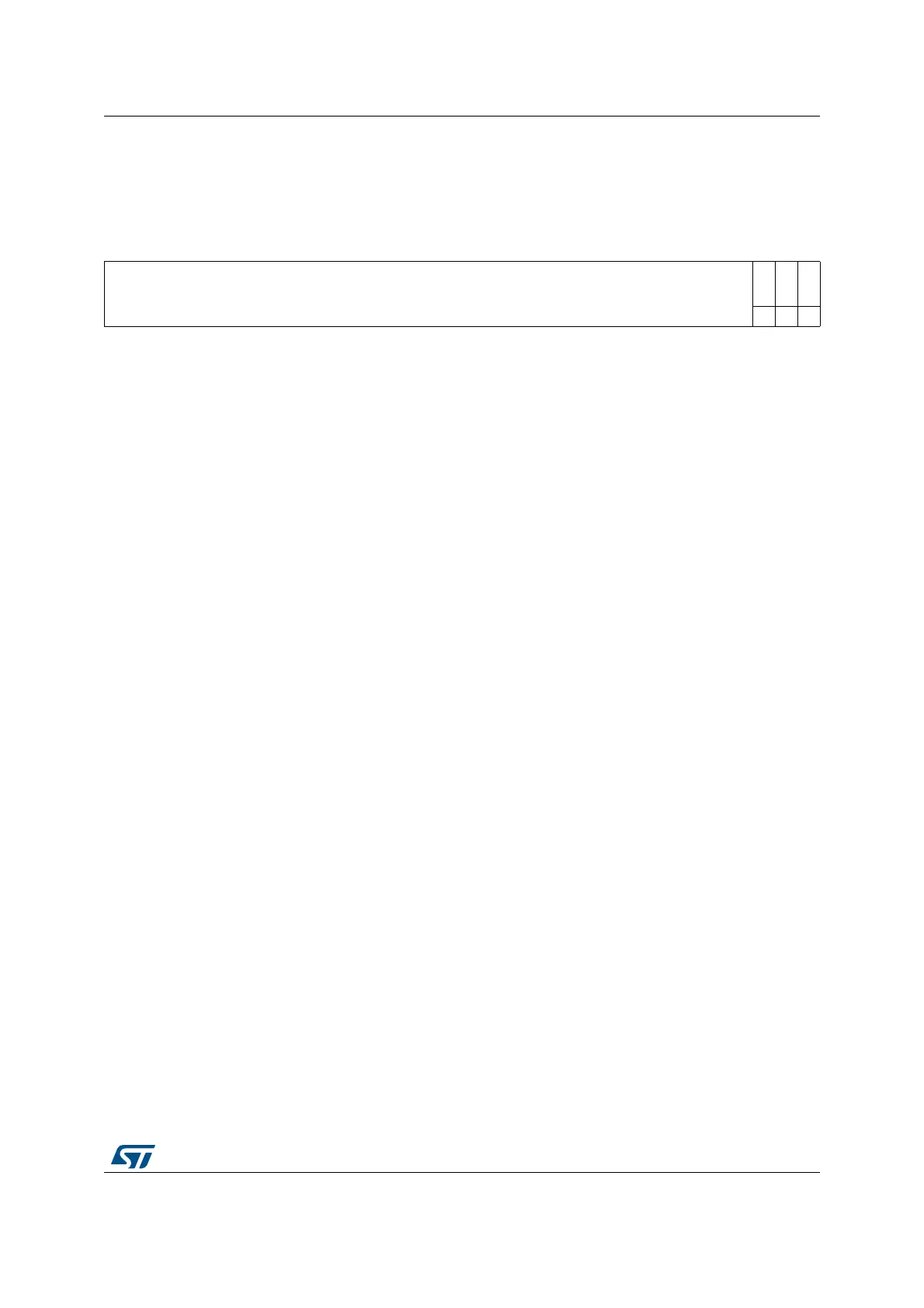

12.8.2 DCMI status register (DCMI_SR)

Address offset: 0x04

Reset value: 0x0000 0x0000

313029282726252423222120191817161514131211109876543210

Reserved

FNE

VSYNC

HSYNC

rrr

Bits 31:3 Reserved, must be kept at reset value.

Bit 2 FNE: FIFO not empty

This bit gives the status of the FIFO

1: FIFO contains valid data

0: FIFO empty

Bit 1 VSYNC

This bit gives the state of the VSYNC pin with the correct programmed polarity.

When embedded synchronization codes are used, the meaning of this bit is the

following:

0: active frame

1: synchronization between frames

In case of embedded synchronization, this bit is meaningful only if the

CAPTURE bit in DCMI_CR is set.

Bit 0 HSYNC

This bit gives the state of the HSYNC pin with the correct programmed polarity.

When embedded synchronization codes are used, the meaning of this bit is the

following:

0: active line

1: synchronization between lines

In case of embedded synchronization, this bit is meaningful only if the

CAPTURE bit in DCMI_CR is set.

Loading...

Loading...