RM0033 Rev 9 845/1381

RM0033 Ethernet (ETH): media access control (MAC) with DMA controller

956

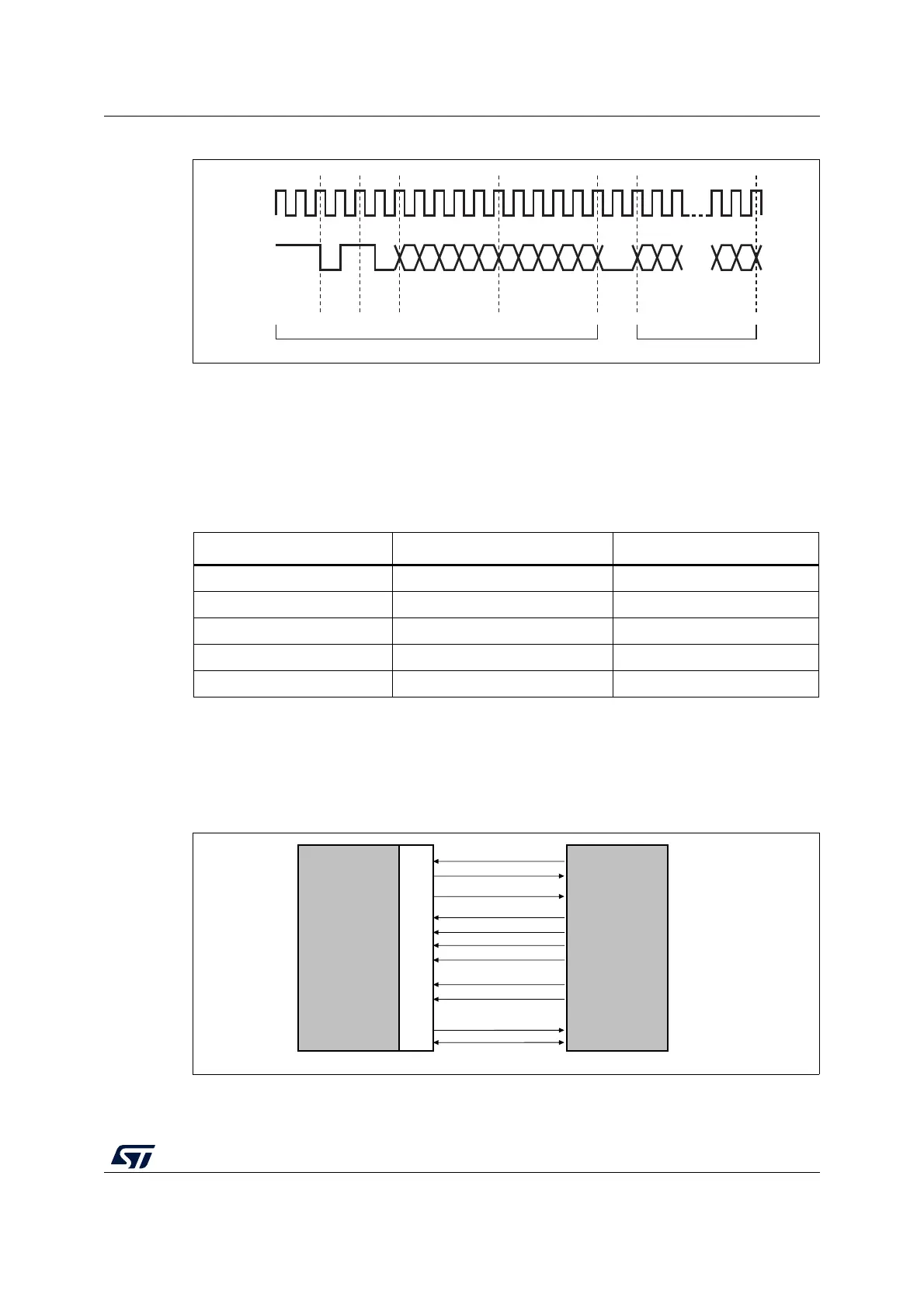

Figure 316. MDIO timing and frame structure - Read cycle

SMI clock selection

The MAC initiates the Management Write/Read operation. The SMI clock is a divided clock

whose source is the application clock (AHB clock). The divide factor depends on the clock

range setting in the MII Address register.

Table 140 shows how to set the clock ranges.

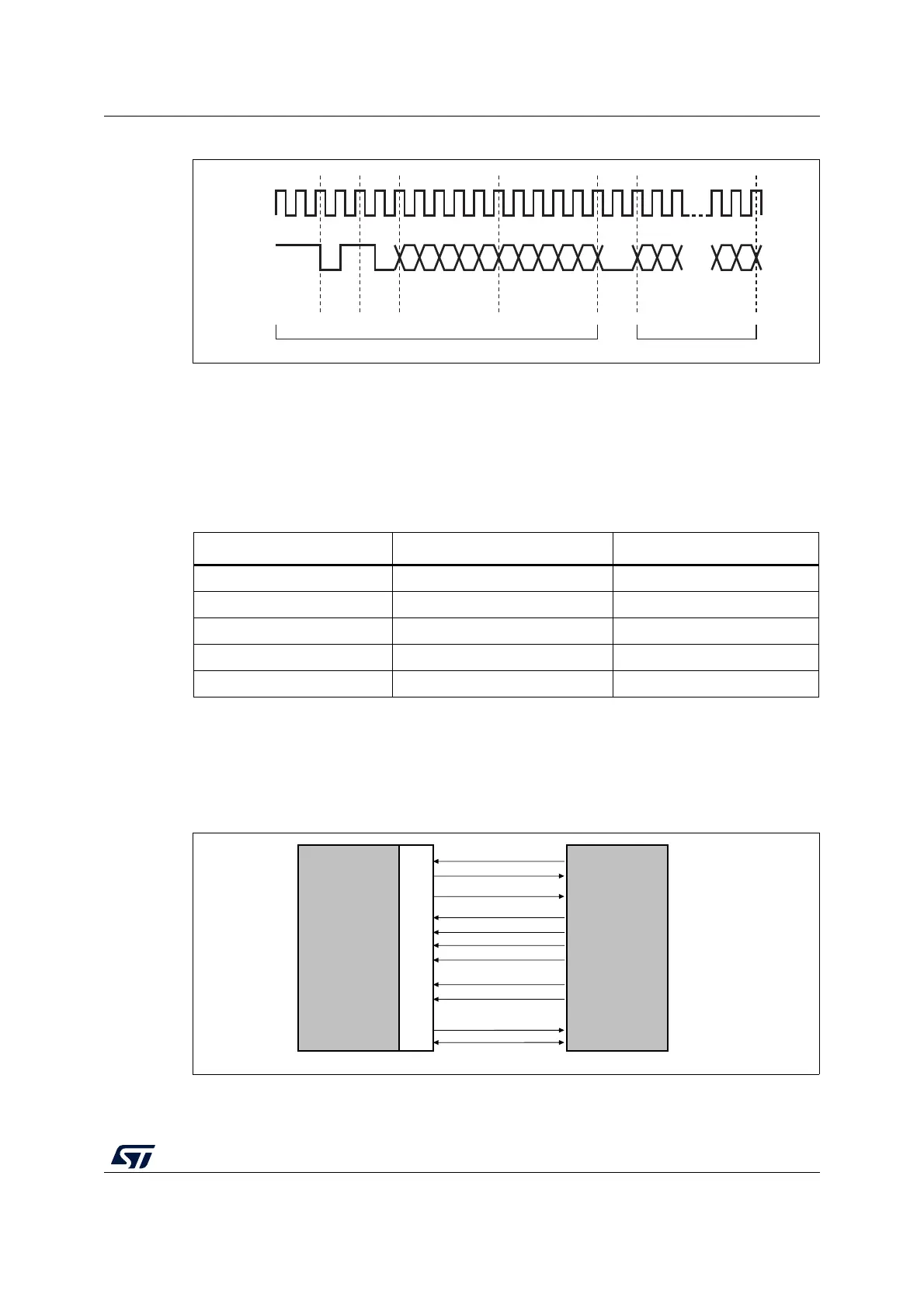

28.4.2 Media-independent interface: MII

The media-independent interface (MII) defines the interconnection between the MAC

sublayer and the PHY for data transfer at 10 Mbit/s and 100 Mbit/s.

Figure 317. Media independent interface signals

Table 140. Clock range

Selection HCLK clock MDC clock

000 60-100 MHz AHB clock / 42

001 100-120 MHz AHB clock / 62

010 20-35 MHz AHB clock / 16

011 35-60 MHz AHB clock / 26

100, 101, 110, 111 Reserved -

MDC

MDIO

32 1's 0 1 1 0

A4 A3 A2 A1 A0 R4 R3 R2 R1 R0

D15 D14

D1 D0

Preamble

Start

of

frame

OP

code

PHY address Register address

Turn

around

data

Data to PHY

ai15627

Data from PHY

MDC

MDIO

RX_DV

CRS

COL

TX_EN

RX_CLK

RXD[3:0]

RX_ER

TX _CLK

TXD[3:0]

External

PHY

ai15622c

802.3 MAC

STM32 MCU

Loading...

Loading...