USB on-the-go high-speed (OTG_HS) RM0033

1160/1381 RM0033 Rev 9

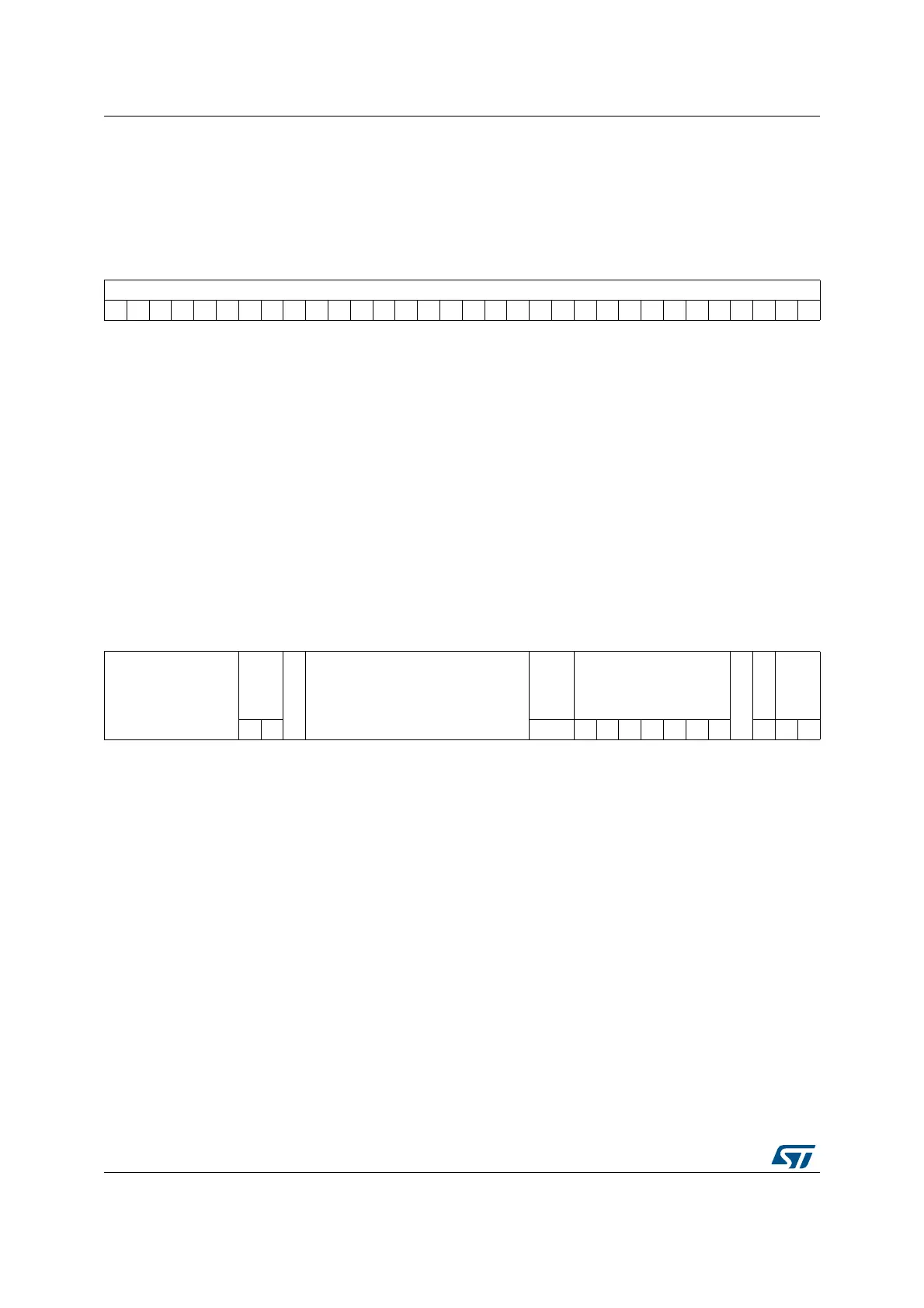

OTG_HS host channel-x DMA address register (OTG_HS_HCDMAx) (x = 0..11,

where x = Channel_number)

Address offset: 0x514 + 0x20 * x

Reset value: 0x0000 0000

30.12.4 Device-mode registers

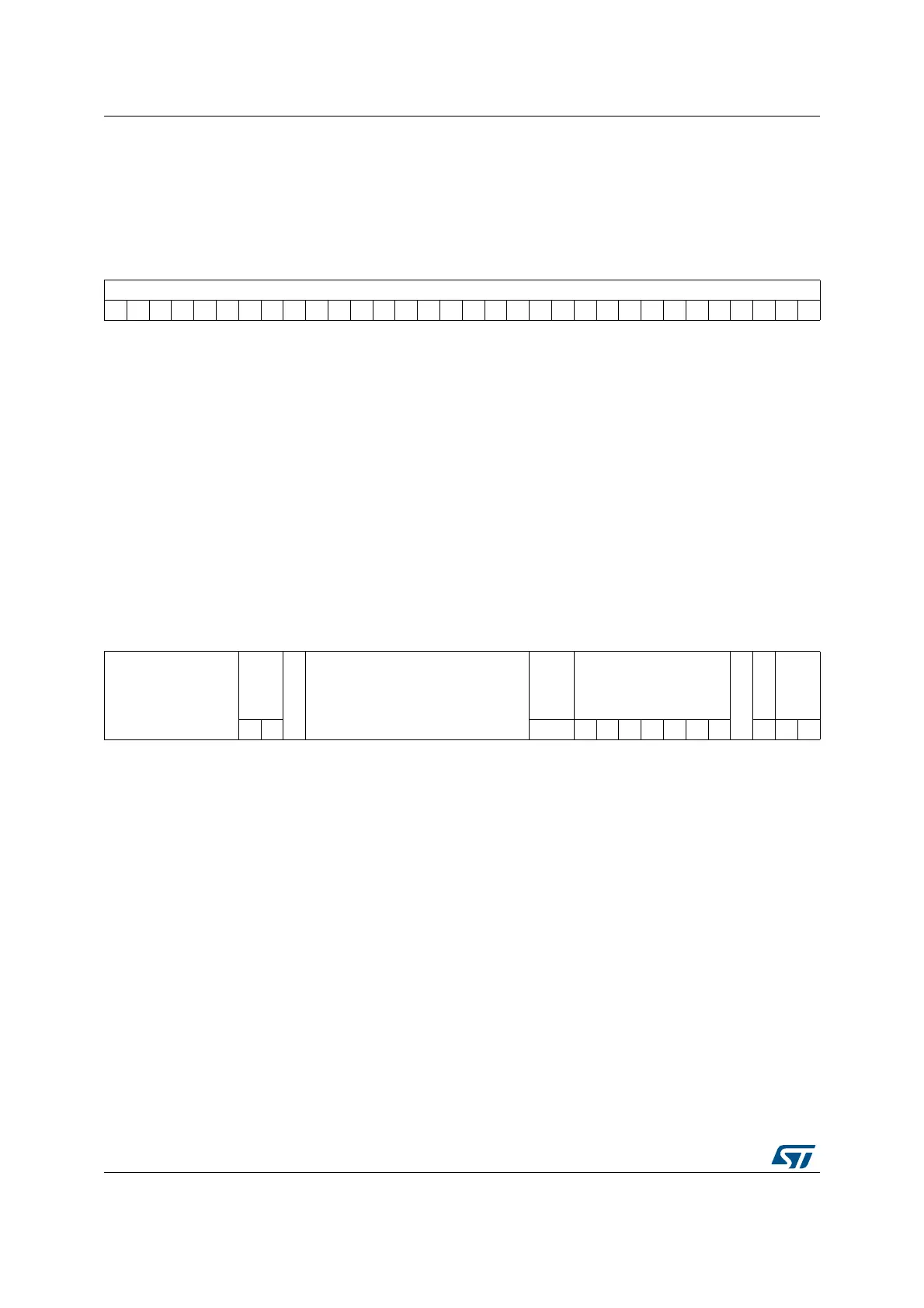

OTG_HS device configuration register (OTG_HS_DCFG)

Address offset: 0x800

Reset value: 0x0220 0000

This register configures the core in peripheral mode after power-on or after certain control

commands or enumeration. Do not make changes to this register after initial programming.

313029282726252423222120191817161514131211109876543210

DMAADDR

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 DMAADDR: DMA address

This field holds the start address in the external memory from which the data for the endpoint

must be fetched or to which it must be stored. This register is incremented on every AHB

transaction.

313029282726252423222120191817161514131211109876543210

Reserved

PERSCHIVL

Reserved

Reserved

PFIVL

DAD

Reserved

NZLSOHSK

DSPD

rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:26 Reserved, must be kept at reset value.

Bits 25:24 PERSCHIVL: Periodic scheduling interval

This field specifies the amount of time the Internal DMA engine must allocate for fetching

periodic IN endpoint data. Based on the number of periodic endpoints, this value must be

specified as 25, 50 or 75% of the (micro)frame.

– When any periodic endpoints are active, the internal DMA engine allocates the

specified amount of time in fetching periodic IN endpoint data

– When no periodic endpoint is active, then the internal DMA engine services

nonperiodic endpoints, ignoring this field

– After the specified time within a (micro)frame, the DMA switches to fetching

nonperiodic endpoints

00: 25% of (micro)frame

01: 50% of (micro)frame

10: 75% of (micro)frame

11: Reserved

Bits 23:13 Reserved, must be kept at reset value.

Loading...

Loading...