Ethernet (ETH): media access control (MAC) with DMA controller RM0033

934/1381 RM0033 Rev 9

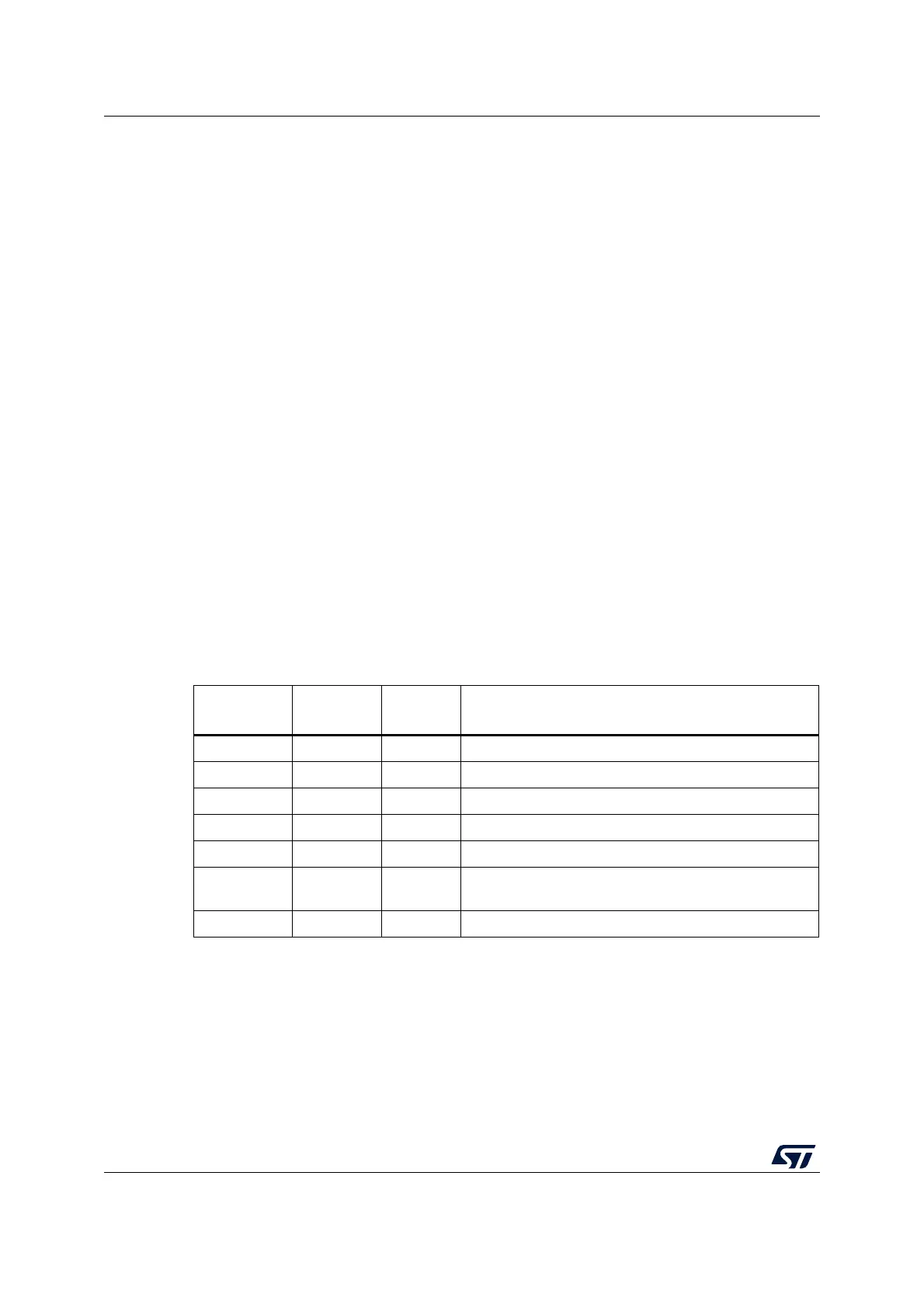

The table below indicates the messages for which a snapshot is taken depending on the

clock, enable master and enable snapshot for event message register settings.

Bit 4 TSITE: Time stamp interrupt trigger enable

When this bit is set, a time stamp interrupt is generated when the system time becomes

greater than the value written in the Target time register. When the Time stamp trigger

interrupt is generated, this bit is cleared.

Bit 3 TSSTU: Time stamp system time update

When this bit is set, the system time is updated (added to or subtracted from) with the value

specified in the Time stamp high update and Time stamp low update registers. Both the

TSSTU and TSSTI bits must be read as zero before you can set this bit. Once the update is

completed in hardware, this bit is cleared.

Bit 2 TSSTI: Time stamp system time initialize

When this bit is set, the system time is initialized (overwritten) with the value specified in the

Time stamp high update and Time stamp low update registers. This bit must be read as zero

before you can set it. When initialization is complete, this bit is cleared.

Bit 1 TSFCU: Time stamp fine or coarse update

When set, this bit indicates that the system time stamp is to be updated using the Fine

Update method. When cleared, it indicates the system time stamp is to be updated using the

Coarse method.

Bit 0 TSE: Time stamp enable

When this bit is set, time stamping is enabled for transmit and receive frames. When this bit

is cleared, the time stamp function is suspended and time stamps are not added for transmit

and receive frames. Because the maintained system time is suspended, you must always

initialize the time stamp feature (system time) after setting this bit high.

Table 147. Time stamp snapshot dependency on registers bits

TSCNT

(bits 17:16)

TSSMRME

(bit 15)

(1)

1. N/A = not applicable.

TSSEME

(bit 14)

Messages for which snapshots are taken

00 or 01 X

(2)

2. X = don’t care.

0 SYNC, Follow_Up, Delay_Req, Delay_Resp

00 or 01 1 1 Delay_Req

00 or 01 0 1 SYNC

10 N/A 0 SYNC, Follow_Up, Delay_Req, Delay_Resp

10 N/A 1 SYNC, Follow_Up

11 N/A 0

SYNC, Follow_Up, Delay_Req, Delay_Resp,

Pdelay_Req, Pdelay_Resp

11 N/A 1 SYNC, Pdelay_Req, Pdelay_Resp

Loading...

Loading...