RM0033 Rev 9 587/1381

RM0033 Real-time clock (RTC)

597

Note: WUT = Wakeup unit counter value. WUT = (0x0000 to 0xFFFF) + 0x10000 added when

WUCKSEL[2:1 = 11].

Bits 7, 6 and 4 of this register can be written in initialization mode only (RTC_ISR/INITF = 1).

Bits 2 to 0 of this register can be written only when RTC_CR WUTE bit = 0 and RTC_ISR

WUTWF bit = 1.

It is recommended not to change the hour during the calendar hour increment as it could

mask the incrementation of the calendar hour.

ADD1H and SUB1H changes are effective in the next second.

To avoid spuriously setting of TSF, TSE must be reset when TSEDGE is changed.

This register is write protected. The write access procedure is described in RTC register

write protection on page 574.

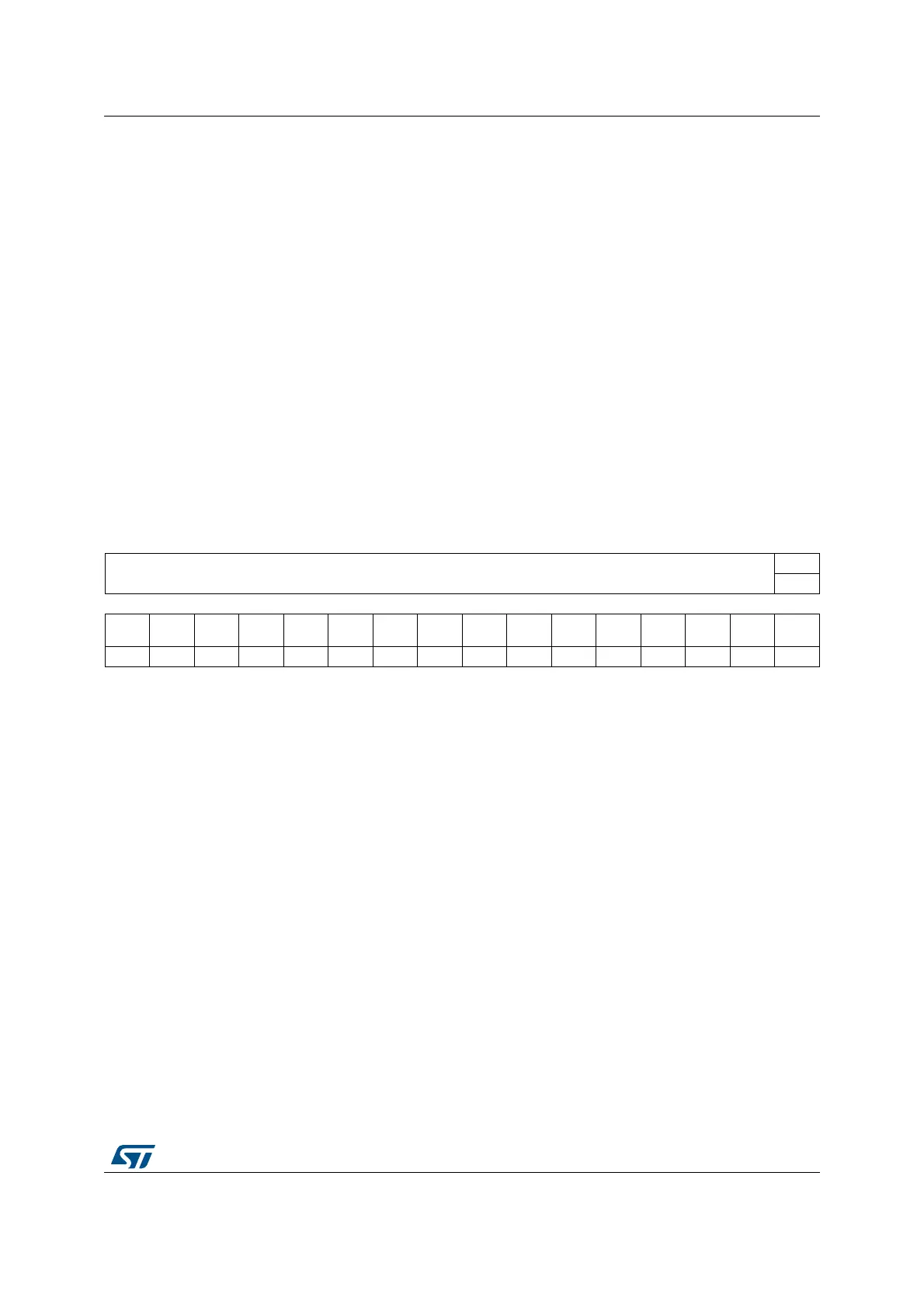

22.6.4 RTC initialization and status register (RTC_ISR)

Address offset: 0x0C

Backup domain reset value: 0x0000 0007

System reset value: Not affected except INIT, INITF and RSF which are cleared to 0.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res.

1514131211109876543210

Res. Res.

TAMP

1F

TSOVF TSF WUTF ALRBF ALRAF INIT INITF RSF INITS Res.

WUT

WF

ALRB

WF

ALRA

WF

rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rw r rc_w0 r r r r

Bits 31:14 Reserved

Bit 13 TAMP1F: Tamper detection flag

This flag is set by hardware when a tamper detection event is detected.

It is cleared by software writing 0.

Bit 12 TSOVF: Timestamp overflow flag

This flag is set by hardware when a timestamp event occurs while TSF is already set.

This flag is cleared by software by writing 0. It is recommended to check and then clear

TSOVF only after clearing the TSF bit. Otherwise, an overflow might not be noticed if a

timestamp event occurs immediately before the TSF bit is cleared.

Bit 11 TSF: Timestamp flag

This flag is set by hardware when a timestamp event occurs.

This flag is cleared by software by writing 0.

Bit 10 WUTF: Wakeup timer flag

This flag is set by hardware when the wakeup auto-reload counter reaches 0.

This flag is cleared by software by writing 0.

This flag must be cleared by software at least 1.5 RTCCLK periods before WUTF is set to 1

again.

Bit 9 ALRBF: Alarm B flag

This flag is set by hardware when the time/date registers (RTC_TR and RTC_DR) match the

Alarm B register (RTC_ALRMBR).

This flag is cleared by software by writing 0.

Loading...

Loading...