Independent watchdog (IWDG) RM0033

498/1381 RM0033 Rev 9

17.4 IWDG registers

Refer to Section 2.2 on page 45 for a list of abbreviations used in register descriptions.

The peripheral registers have to be accessed by half-words (16 bits) or words (32 bits).

17.4.1 Key register (IWDG_KR)

Address offset: 0x00

Reset value: 0x0000 0000 (reset by Standby mode)

17.4.2 Prescaler register (IWDG_PR)

Address offset: 0x04

Reset value: 0x0000 0000

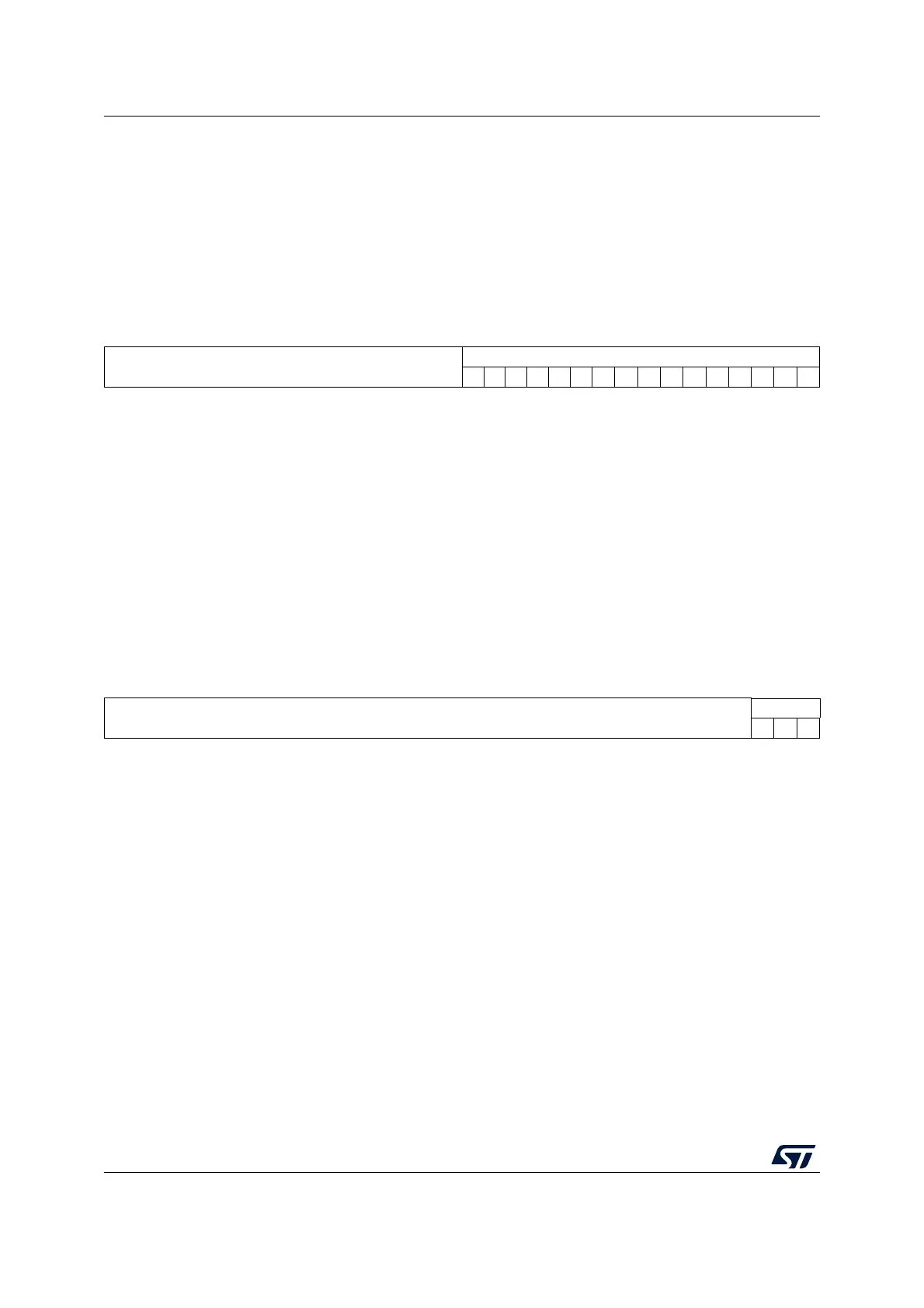

313029282726252423222120191817161514131211109876543210

Reserved

KEY[15:0]

wwwwwww w wwwwwwww

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 KEY[15:0]: Key value (write only, read 0000h)

These bits must be written by software at regular intervals with the key value AAAAh,

otherwise the watchdog generates a reset when the counter reaches 0.

Writing the key value 5555h to enable access to the IWDG_PR and IWDG_RLR registers

(see Section 17.3.2)

Writing the key value CCCCh starts the watchdog (except if the hardware watchdog option is

selected)

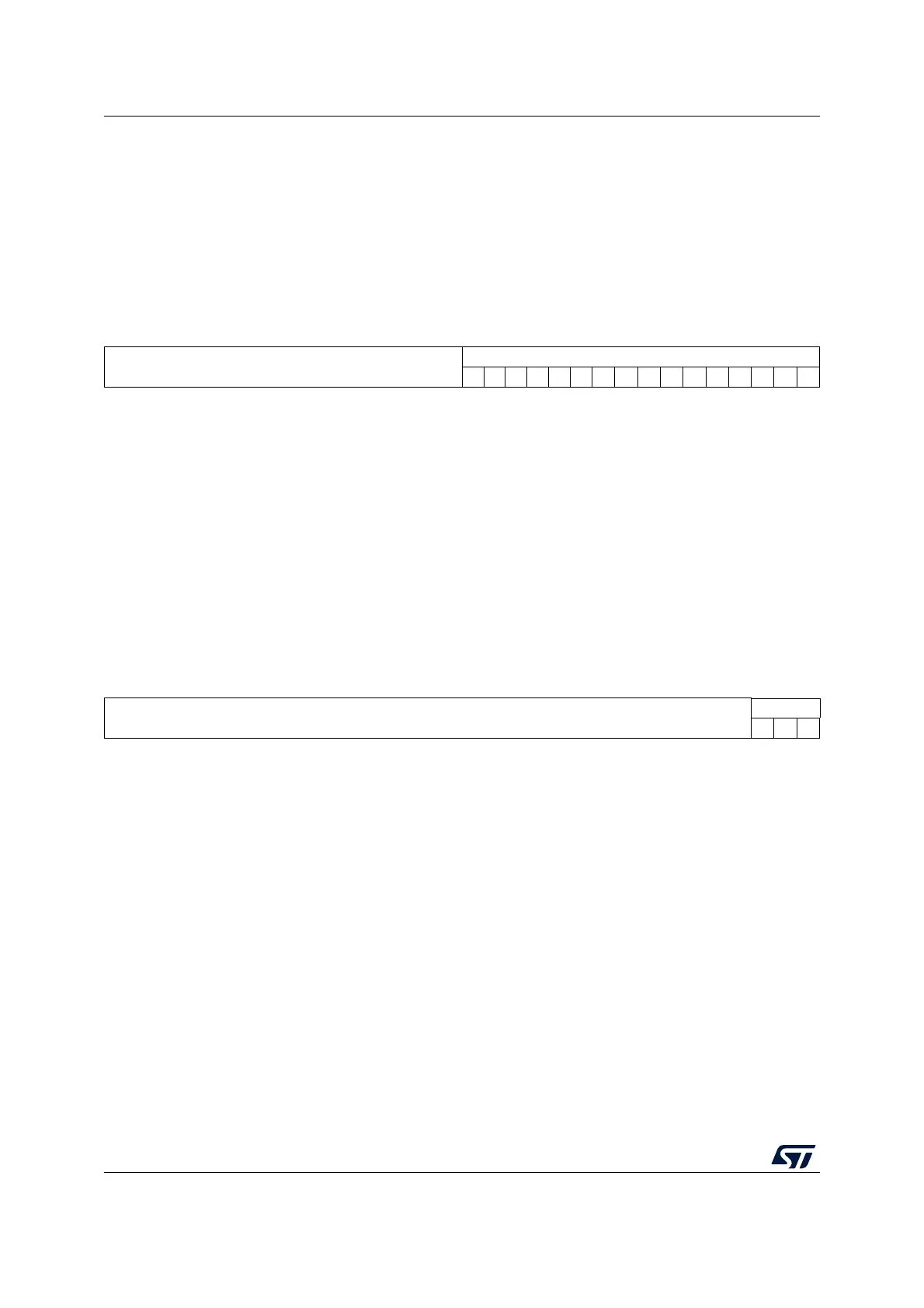

313029282726252423222120191817161514131211109876543210

Reserved

PR[2:0]

rw rw rw

Bits 31:3 Reserved, must be kept at reset value.

Bits 2:0 PR[2:0]: Prescaler divider

These bits are write access protected seeSection 17.3.2. They are written by software to

select the prescaler divider feeding the counter clock. PVU bit of IWDG_SR must be reset in

order to be able to change the prescaler divider.

000: divider /4

001: divider /8

010: divider /16

011: divider /32

100: divider /64

101: divider /128

110: divider /256

111: divider /256

Note: Reading this register returns the prescaler value from the VDD voltage domain. This

value may not be up to date/valid if a write operation to this register is ongoing. For this

reason the value read from this register is valid only when the PVU bit in the IWDG_SR

register is reset.

Loading...

Loading...