Ethernet (ETH): media access control (MAC) with DMA controller RM0033

932/1381 RM0033 Rev 9

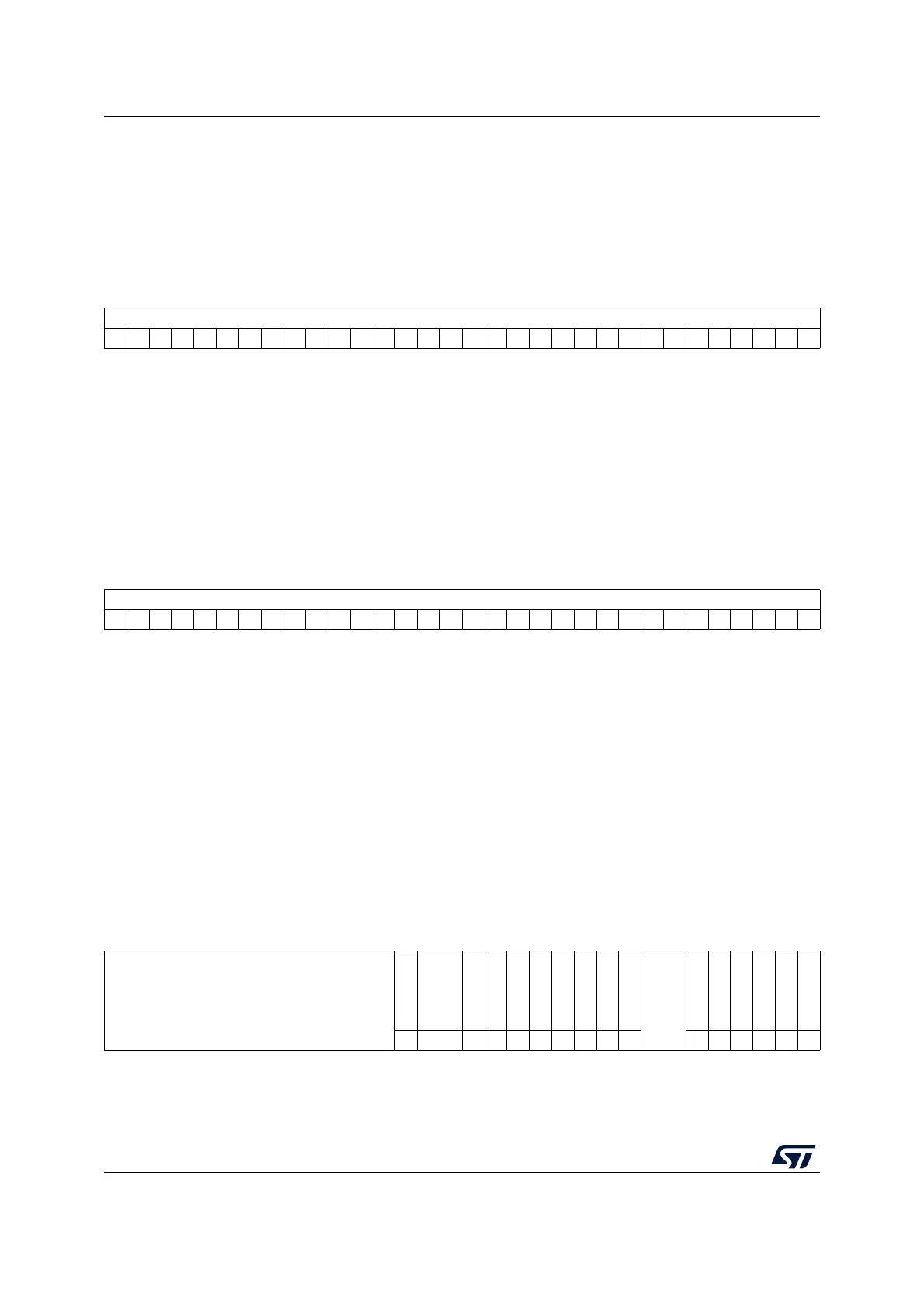

Ethernet MMC received frames with alignment error counter register

(ETH_MMCRFAECR)

Address offset: 0x0198

Reset value: 0x0000 0000

This register contains the number of frames received with alignment (dribble) error.

MMC received good unicast frames counter register (ETH_MMCRGUFCR)

Address offset: 0x01C4

Reset value: 0x0000 0000

This register contains the number of good unicast frames received.

28.8.3 IEEE 1588 time stamp registers

This section describes the registers required to support precision network clock

synchronization functions under the IEEE 1588 standard.

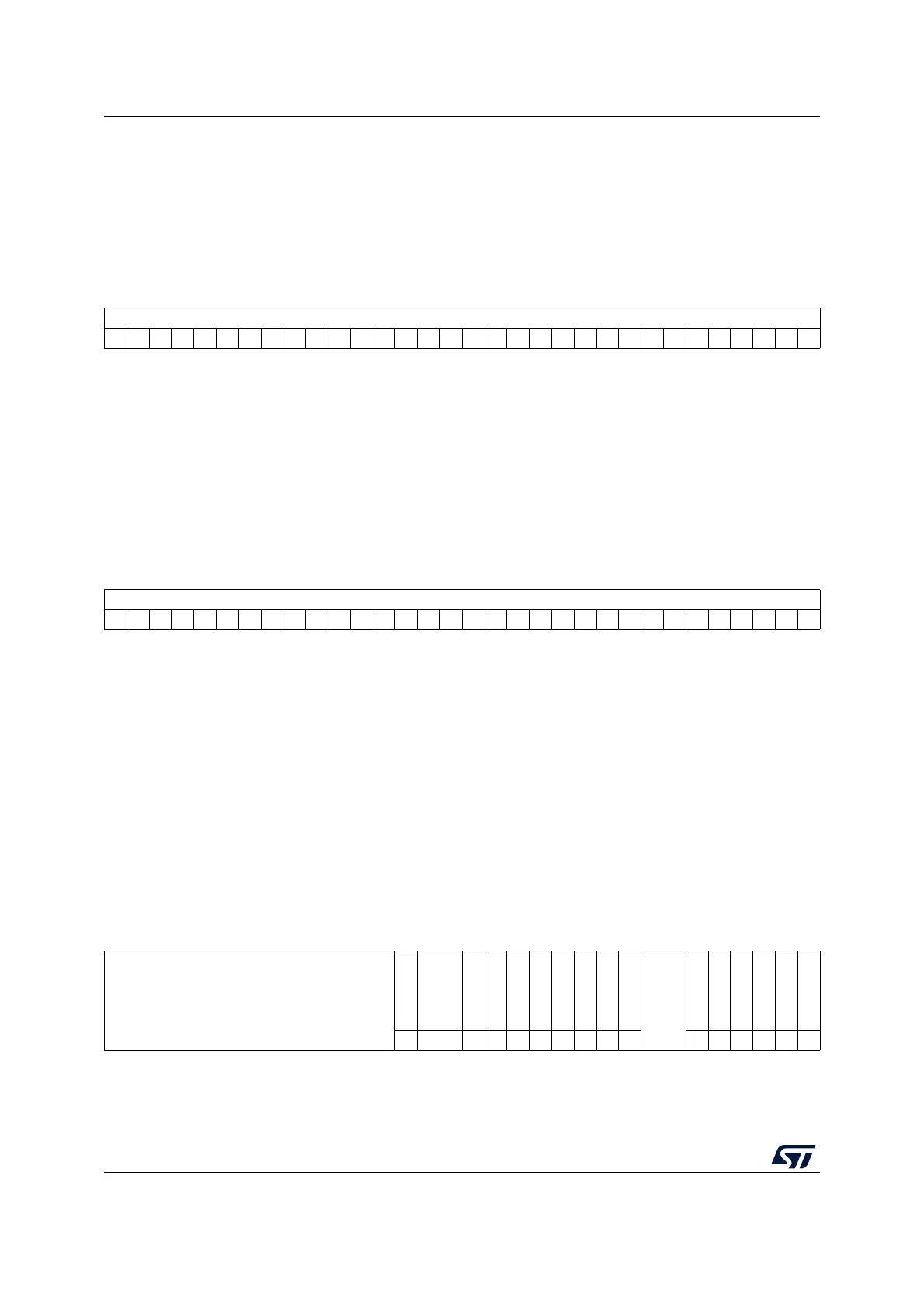

Ethernet PTP time stamp control register (ETH_PTPTSCR)

Address offset: 0x0700

Reset value: 0x0000 00002000

This register controls the time stamp generation and update logic.

313029282726252423222120191817161514131211109876543210

RFAEC

rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr

Bits 31:0 RFAEC: Received frames alignment error counter

Received frames with alignment error counter

313029282726252423222120191817161514131211109876543210

RGUFC

rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr

Bits 31:0 RGUFC: Received good unicast frames counter

313029282726252423222120191817161514131211109876543210

Reserved

TSPFFMAE

TSCNT

TSSMRME

TSSEME

TSSIPV4FE

TSSIPV6FE

TSSPTPOEFE

TSPTPPSV2E

TSSSR

TSSARFE

Reserved

TTSARU

TSITE

TSSTU

TSSTI

TSFCU

TSE

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...