RM0033 Rev 9 901/1381

RM0033 Ethernet (ETH): media access control (MAC) with DMA controller

956

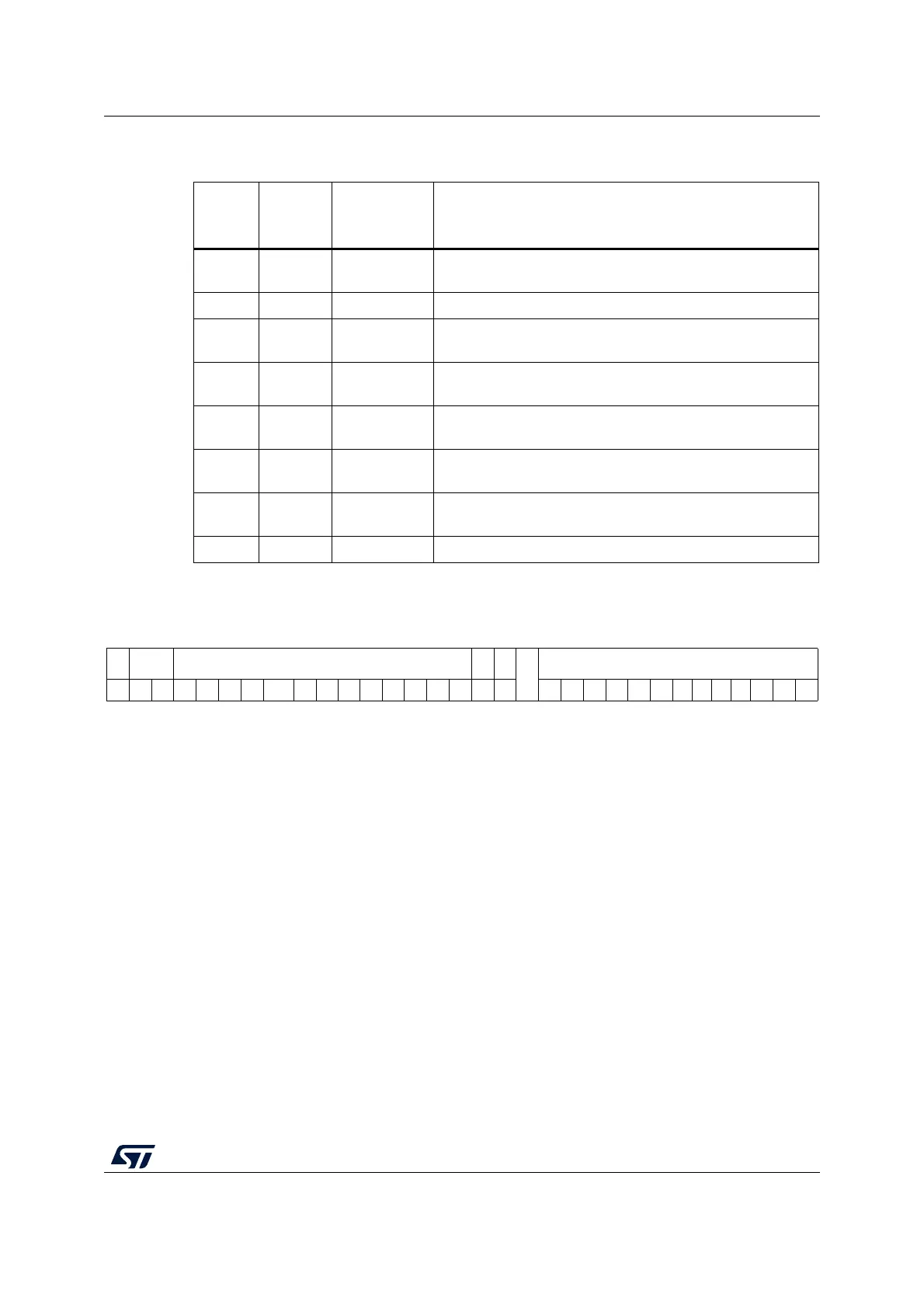

• RDES1: Receive descriptor Word1

Table 146. Receive descriptor 0 - encoding for bits 7, 5 and 0 (normal descriptor

format only, EDFE=0)

Bit 5:

frame

type

Bit 7: IPC

checksum

error

Bit 0: payload

checksum

error

Frame status

00 0

IEEE 802.3 Type frame (Length field value is less than

0x0600.)

1 0 0 IPv4/IPv6 Type frame, no checksum error detected

10 1

IPv4/IPv6 Type frame with a payload checksum error (as described

for PCE) detected

11 0

IPv4/IPv6 Type frame with an IP header checksum error (as

described for IPC CE) detected

11 1

IPv4/IPv6 Type frame with both IP header and payload checksum

errors detected

00 1

IPv4/IPv6 Type frame with no IP header checksum error and the

payload check bypassed, due to an unsupported payload

01 1

A Type frame that is neither IPv4 or IPv6 (the checksum offload

engine bypasses checksum completely.)

0 1 0 Reserved

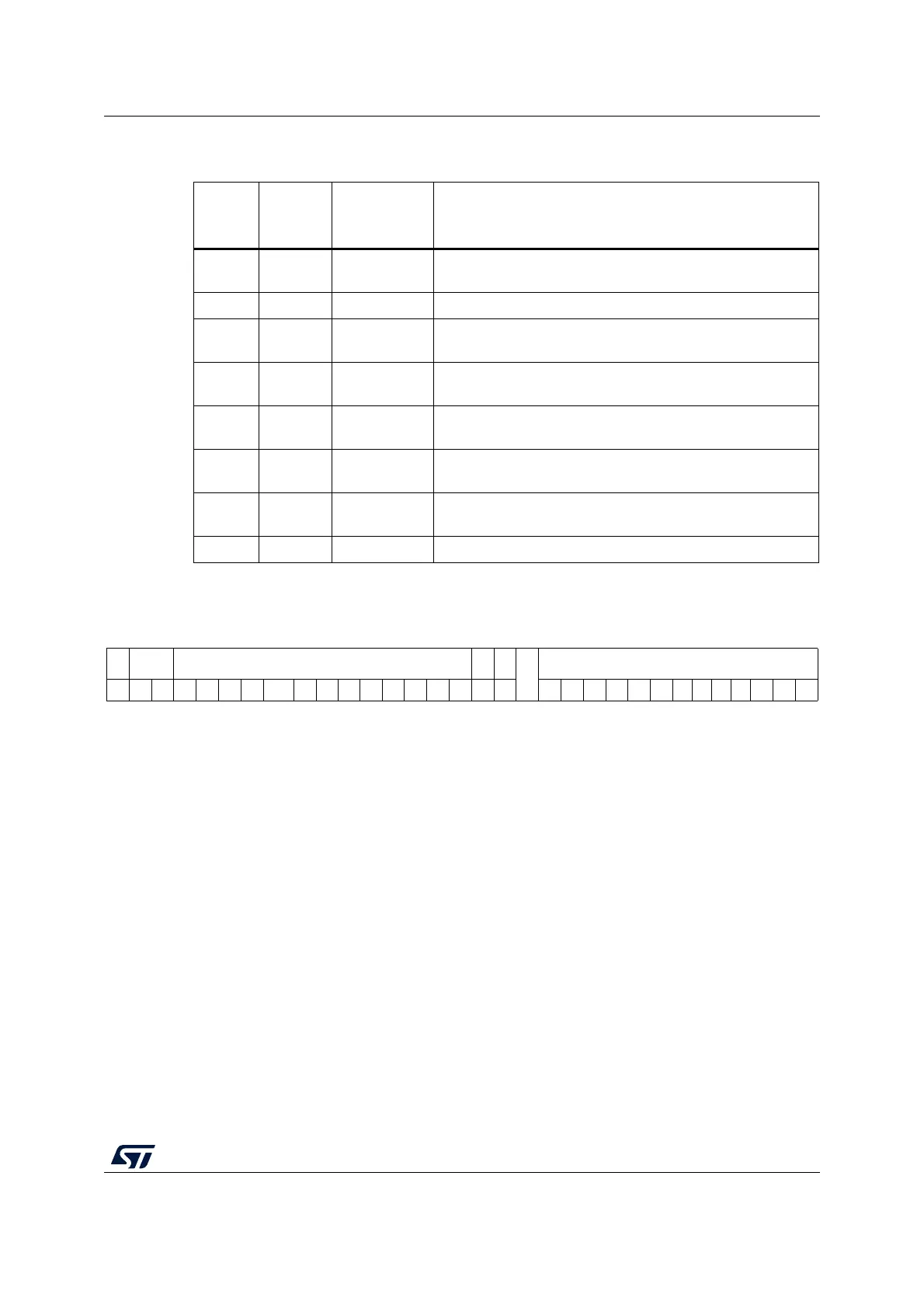

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

DIC

RBS2 RBS2

RER

RCH

Reserved

RBS

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bit 31 DIC: Disable interrupt on completion

When set, this bit prevents setting the Status register’s RS bit (CSR5[6]) for the received frame

ending in the buffer indicated by this descriptor. This, in turn, disables the assertion of the interrupt to

Host due to RS for that frame.

Bits 30:29 Reserved, must be kept at reset value.

Bits 28:16 RBS2: Receive buffer 2 size

These bits indicate the second data buffer size, in bytes. The buffer size must be a multiple of 4,

8, or 16, depending on the bus widths (32, 64 or 128, respectively), even if the value of RDES3

(buffer2 address pointer) is not aligned to bus width. If the buffer size is not an appropriate multiple

of 4, 8 or 16, the resulting behavior is undefined. This field is not valid if RDES1 [14] is set.

Bit 15 RER: Receive end of ring

When set, this bit indicates that the descriptor list reached its final descriptor. The DMA returns to the

base address of the list, creating a descriptor ring.

Loading...

Loading...